Fターム[5J106EE01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 検出回路 (618)

Fターム[5J106EE01]の下位に属するFターム

Fターム[5J106EE01]に分類される特許

1 - 20 / 94

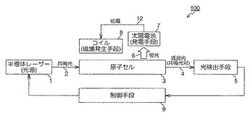

原子発振器

【課題】専用の電源を不要として、小型化と省エネを実現した原子発振器を提供する。

【解決手段】本実施形態に係る原子発振器100は、アルカリ金属原子(Na、Rb、Cs)が封入された原子セル3と、アルカリ金属原子に電磁誘起透過現象を発現させるための共鳴光2を照射する半導体レーザー(光源)1と、原子セル3を透過した透過光(共鳴光対)4を検出する光検出手段5と、アルカリ金属原子が発する蛍光6の強度に応じた電力を発電する太陽電池(発電手段)7と、太陽電池7から供給された電力によってアルカリ金属原子に与える磁場を発生するコイル(磁場発生手段)8と、光検出手段5で検知した信号を同期制御する制御手段9と、を備えて構成されている。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティング20aに電圧を印加する電圧印加部20bと、を有する。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

位相固定ループ及びその動作方法

【課題】位相固定ループのロッキングタイムを減らすことができる、特にターゲット値(出力クロックの目標周波数)が変化しても常に短いロッキングタイムを有する位相固定ループ及びその動作方法を提供する。

【解決手段】位相固定ループは、入力クロックCLK_INの位相とフィードバッククロックCLK_FBの位相とを比較する位相比較部310と、位相比較部310の比較結果UP,DNに応じて周波数制御信号DCO_CONTROL_SIGNALSを生成する制御部330と、周波数制御信号DCO_CONTROL_SIGNALSに応答して出力クロックCLK_OUTを生成するオシレータ部340と、入力クロックCLK_INの周波数を検出して、検出結果に応じて初期値INIT_VALUEを制御部330に提供する初期値提供部350とを備える。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

半導体回路

【課題】DCC回路を備えたDLL回路の消費電力を低減させる。

【解決手段】制御信号DCCENに基づいて活性化・非活性化が制御されるデューティ変更検出回路21であって、入力されたクロック信号に基づいて生成されたクロック信号のデューティとあらかじめ設定されたデューティとを比較しその結果を出力するデューティ変更検出回路21と、デューティ変更検出回路の出力が生成されたクロック信号のデューティがあらかじめ設定されたデューティである目標値近傍にあることを示すときにはデューティ変更検出回路21を非活性化する制御信号DCCENを出力すると共に目標値近傍に無いときにはデューティ変更検出回路21を活性化する制御信号DCCENを出力するデューティ判定回路23とを備える。

(もっと読む)

PLL回路

【課題】出力クロック信号のロングタームジッタを抑制するPLL回路を提供する。

【解決手段】位相比較器、チャージポンプ回路、ループフィルタ、及び電圧制御発振器を有するPLL回路において、基準クロック信号と帰還クロック信号との位相差が所定の閾値より大きい場合には、位相差の単位量当たりに対する変化を小さくして位相差に応じた出力電流を出力し、位相差が所定の閾値以下である場合には、位相差の単位量当たりに対する変化を大きくして位相差に応じた出力電流を出力するようにして、ロック後のループ帯域を広げることができるようにする。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

ジッタ除去回路

【課題】従来では、基準クロック生成回路が生成するクロックにジッタが発生するという問題があった。

【解決手段】本発明にかかるジッタ除去回路は、基準クロック51のジッタを除去するジッタ除去回路であって、サンプリングクロック52に同期して基準クロック51のエッジを検出するラッチ回路12と、基準クロック51のエッジ間隔をカウントするカウンタ13と、各エッジ間隔のカウント数に基づいて基準クロック51の位相を調整する位相調整回路14と、を備える。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

原子発振器及び原子発振器の制御方法

【課題】最大強度のEIT信号が検出でき、S/Nを向上して周波数の安定化を図ること

ができる原子発振器を提供する。

【解決手段】この原子発振器100は、アルカリ金属原子に電磁誘起透過現象(EIT現

象)を発生させるための共鳴光対を生成する光源1と、光源1からの光の波長により光の

吸収量を変化させるアルカリ金属入りセル2と、光源1に高周波信号を供給して共鳴光対

を生成するサイドバンド発生手段5と、光源1に直流信号を供給して共鳴光対の中心周波

数を可変する中心波長可変手段4と、アルカリ金属原子を透過した共鳴光対を検出し、透

過した共鳴光対の強度に応じた検出信号を出力する光検出手段3と、共鳴光対の中心周波

数を可変したときの検出信号の最小値を検出する吸収検出手段6と、サイドバンド発生手

段5から出力される高周波信号の供給又は停止を制御する信号処理手段8と、を備えて構

成されている。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

周波数同期装置、受信機および周波数同期方法

【課題】インパルス状の外乱が生じる環境でも、精度の良い周波数同期を確立することができる周波数同期装置を得ること。

【解決手段】再生周波数を受信信号に同期させる周波数同期制御を行う周波数同期装置であって、受信信号に基づいて周波数偏差を求める周波数偏差検出部2と、周波数偏差の時間変化量を算出する差分部3と、時間変化量に基づいて、前記周波数偏差を周波数制御値として用いるか否かを示す制御値選択信号を生成する観測部6と、制御値選択信号が周波数偏差を周波数制御値として用いないことを示す値であった場合には、過去の周波数制御値に基づいてその時点での周波数制御値の推定値である推定制御値を求め、求めた推定制御値を周波数制御値として選択するホールド部7と、を備える。

(もっと読む)

1 - 20 / 94

[ Back to top ]