Fターム[5J106JJ05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 周波数変換回路 (57)

Fターム[5J106JJ05]に分類される特許

1 - 20 / 57

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

可変分周装置

【課題】クロック信号が高速化した場合でも対応することのできる可変分周装置を得る。

【解決手段】可変分周回路101は、クロック信号Clk_aを入力し、クロック信号Clk_aに対するP(Pは2以上の整数)またはP+1の分周した信号Do1を出力する。可変分周回路102は、クロック信号Clk_aと逆相になるクロック信号Clk_bを入力し、クロック信号Clk_bに対するPまたはP+1の分周した信号Do2を出力する。経路切り替え回路103は、信号Do1,Do2を入力し、経路選択信号MuxContにより信号Do1,Do2のうちいずれか一方を選択し出力する。

(もっと読む)

出力信号制御装置、出力信号制御方法および出力信号制御プログラム

【課題】入力信号を遅延させて出力信号を作成する際に、入力信号の変動が原因で出力信号の遅延が規定値内に納まらない場合であっても、この出力信号によるエラーの発生の抑制が可能な出力信号制御装置、方法およびプログラムを得ること。

【解決手段】位相差許容範囲判別手段12は、位相差測定手段11が測定した出力信号の位相差がこの出力信号を入力する回路で許容範囲内であるかを判別する。出力制御手段13は、許容範囲内でないと判別する状態で出力信号の出力を遮断し、許容範囲内となった段階で出力を開始する。

(もっと読む)

分周回路及び集積回路

【課題】分周器の発振を防止する分周回路を提供する。

【解決手段】クロック信号Vcを所定の分周比にて分周する分周器20を備え、分周器の発振を防止する分周回路1であって、クロック信号のピーク電圧Vcpを検出してピーク値を保持するピーク検出器30と、分周器が正常動作するために必要なクロック信号の振幅vpに対応した参照電圧Vrefを出力する参照電圧発生器40と、ピーク検出器により検出されたピーク値と参照電圧とを比較する比較器50と、を備え、分周器に分周開始を指示する制御信号を入力する制御端子を備え、制御端子に比較器の出力信号Veを接続し、ピーク値が参照電圧を超えたときに、比較器は、分周器の制御端子に分周開始を指示する制御信号を出力する

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

周波数シンセサイザ

【課題】設計が容易で、かつノイズ特性を良好にする。

【解決手段】周波数foutの出力信号Soutを生成するVCO5、周波数f1の低周波信号S1を生成する低周波信号生成部3、周波数f2の高周波信号S2を生成する高周波信号生成部4、ミキサ部6、ミキシング信号Smix中の差周波数信号Sdiを通過させる低域フィルタ部7、比較用信号S4を出力する信号処理部10、位相比較部8およびループフィルタ9を備え、信号処理部10は、周波数f2が新たに設定された際に、fout<f2のときには比較用信号S4の出力を停止し、fout≧f2で、かつ差周波数信号Sdiの絶対周波数fdiが低域フィルタ部7のカットオフ周波数fco以上のときには周波数f3(>f1)の基準信号S3を比較用信号S4として出力し、fout≧f2で、かつfdi<fcoのときには差周波数信号Sdiを比較用信号S4として出力する。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

PLL装置及び不要周波数回避方法

【課題】PLL装置において、不要周波数の影響を、無線性能に影響を与えることなく回避できるようにする。

【解決手段】電圧制御発振器3、4と、基準信号に基づく第1信号及び電圧制御発振器の出力信号に基づく第2信号の両位相を比較し、位相差を示す位相差信号を出力する位相比較器1と、位相差信号に基づき、両位相を同期させる制御電圧を電圧制御発振器に印加するループフィルタ2とを備え、所定の目的周波数を得るPLL装置において、目的周波数を中心とする所定の周波数範囲内に不要周波数が存在する場合に、不要周波数を該周波数範囲外のものとするために基準信号の周波数を変更する基準周波数変更手段5と、基準信号の周波数の変更にも拘わらず目的周波数の出力が維持されるように、第1信号又は第2信号を生成する際の分周比を変更する分周比変更手段5とを設ける。

(もっと読む)

分周器

【課題】 動作周波数が高められた分周器を提供する。

【解決手段】 動作制御信号ENBが‘H’レベルに遷移し、クロック信号VCO,分周信号VCO_div2が‘L’レベル,‘H’レベルで停止した場合、3入力ナンドゲート14から出力された制御信号Aが‘L’レベルとなり、イクスクルーシブノアゲート10から出力されるトリガ信号VCO_delayが‘H’レベルとなる。トリガ信号VCO_delayはフリップフロップ11_1のトリガ端子Tに入力されており、フリップフロップ11_1から出力されている分周信号VCO_div2を‘H’レベルから‘L’レベルに遷移して、フリップフロップ11_1をリセット状態にする。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

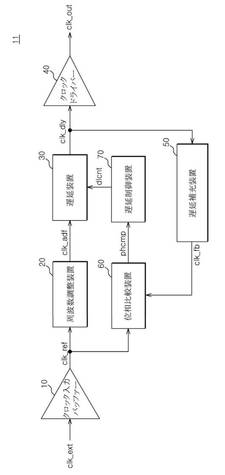

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】 インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】 インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】周波数変動の大きな基準発振器を用いて、周波数変動を抑制した局部発振信号及び分周逓倍信号を出力するシンセサイザを小型に実現すること。

【解決手段】本発明のシンセサイザ2は、基準発振器3から出力された基準発振信号を基に局部発振信号を生成して周波数変換部5に入力するとともに、周波数補償部7から出力された周波数補償信号を基に局部発振信号の周波数補償を行うシンセサイザ2であって、局部発振信号を分周又は逓倍した分周逓倍信号を、周波数変換部5の出力側に接続された後段回路部6に入力する分周逓倍部2aを有する。この構成により、シンセサイザ2が周波数変動を補償した局部発振信号を出力するとともに、この局部発振信号を分周又は逓倍して分周逓倍信号を生成することにより、少なくとも1つのシンセサイザで、局部発振信号及び分周逓倍信号の周波数変動を補償することができる。

(もっと読む)

シンセサイザと、これを用いた受信装置、および電子機器

【課題】精度の高い発振周波数を生み出す事ができるシンセサイザを提供する事を目的とする。

【解決手段】シンセサイザ1は、基準発振器2からの基準発振信号が入力される比較器4と、比較器4の出力信号に基づいて発振信号を出力する電圧制御発振器5と、この電圧制御発振器5の出力信号を制御部7からの制御信号に基づいて分周する第2分周器6とを備えており、比較器4は、第2分周器6からの出力信号と基準発振器2からの出力信号とを比較してこの比較結果を示す信号を電圧制御発振器5に出力し、シンセサイザ1を用いる電子機器の使用状態に基づいて、第2分周器6の分周比の値が決められている。これにより、温度検出部8とMEMS振動子11との間の温度差に起因したシンセサイザの発振周波数誤差を無くす事ができる。

(もっと読む)

1 - 20 / 57

[ Back to top ]