Fターム[5J106RR20]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | スイッチ・セレクタ (90)

Fターム[5J106RR20]に分類される特許

1 - 20 / 90

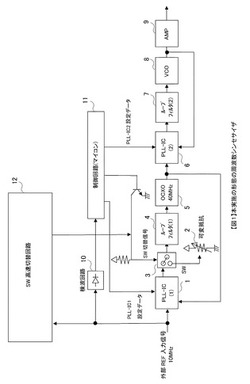

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

可変分周装置

【課題】クロック信号が高速化した場合でも対応することのできる可変分周装置を得る。

【解決手段】可変分周回路101は、クロック信号Clk_aを入力し、クロック信号Clk_aに対するP(Pは2以上の整数)またはP+1の分周した信号Do1を出力する。可変分周回路102は、クロック信号Clk_aと逆相になるクロック信号Clk_bを入力し、クロック信号Clk_bに対するPまたはP+1の分周した信号Do2を出力する。経路切り替え回路103は、信号Do1,Do2を入力し、経路選択信号MuxContにより信号Do1,Do2のうちいずれか一方を選択し出力する。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

無線通信装置

【課題】周波数シンセサイザによる周波数信号を用いる無線通信装置の消費電力を低減する。

【解決手段】受信部が、受信した無線信号に基づく信号と周波数信号とを混合する第1ミキサと、当該第1ミキサの出力とローカル信号とを混合する第2ミキサと、当該第2ミキサの出力を復調して復調信号を生成する復調段とを含み、周波数シンセサイザが、制御入力電圧の変動に応じた周波数の周波数信号を生成するVCOと、当該VCOの出力周波数信号を分周して得られた信号と基準クロック信号との位相差に応じた電圧を制御入力電圧とするフィードバック回路と、からなり、当該VCOは、バイアス電流が大となるほど高い周波数で動作可能となる可変周波数発振器であって、当該バイアス電流が当該モード指定に応じて制御される無線通信装置。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

1 - 20 / 90

[ Back to top ]