Fターム[5J500AK47]の内容

Fターム[5J500AK47]に分類される特許

21 - 40 / 565

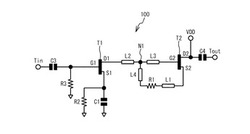

電子回路

【課題】、高出力動作が可能なカレントリユース電子回路を提供すること。

【解決手段】第1端子、第2端子および制御端子を有し、前記第1端子が接地された第1トランジスタT1と、第1端子、第2端子および制御端子を有し、前記制御端子に前記第1トランジスタの第2端子が接続され、前記第1端子が前記第1トランジスタの前記第2端子と高周波的に接続され、前記第2端子に直流電源が接続される第2トランジスタT2と、前記第1トランジスタの第2端子と前記第2トランジスタの制御端子との間のノードに一端が接続され、他端が前記第2トランジスタの第1端子に接続された第1抵抗R1と、を具備した電子回路。

(もっと読む)

受光増幅回路及びそれを用いた光ピックアップ装置

【課題】光ディスクの高倍速化により高い周波数応答特性が必要な場合においても、RF信号成分の信号振幅を低下させない受光増幅回路を提供することを目的とする。

【解決手段】入力された光電流を電圧に変換するとともに、変換した電圧のうち第1カットオフ周波数より低い周波数に対応する電圧のみを出力する電流電圧変換アンプ102と、電流電圧変換アンプ102の後段に接続され、電流電圧変換アンプ102から出力された電圧のうち第2カットオフ周波数より低い周波数に対応する電圧のみを出力するCRローパスフィルタ回路103と、CRローパスフィルタ回路103の後段に接続され、CRローパスフィルタ回路103から出力された電圧を増幅する電圧増幅アンプ104と、少なくとも電圧増幅アンプ104と接続され、電圧増幅アンプ104から出力された電圧を加算増幅するRF増幅加算アンプ105と、を備える。

(もっと読む)

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

可変利得増幅回路およびそれを用いた受信回路

【課題】連続して入力される信号の増幅または減衰が可能であるとともに、広い利得可変範囲及び高い線形性を実現することが出来る可変利得増幅回路およびそれを用いた受信回路を提供する。

【解決手段】本発明の可変利得増幅回路では、増幅トランジスタのゲートに入力される信号のレベルを低くする(図1(a)の状態(A)〜(D))ために、第1可変利得増幅部の利得が最小になったとき、第2可変利得増幅部が備える第1抵抗および第2抵抗にバイアス電圧を印加する。

(もっと読む)

電子回路及び光受光回路

【課題】 入出力信号のオフセットを補償して、入力電流が増大しても増幅動作を行うことができる電子回路及び光受光回路を提供する。

【解決手段】 本発明の電子回路30は、相補的な入力電流を、相補的な電圧信号に変換して出力する差動トランスインピーダンスアンプ10と、出力を入力し、出力が差動トランスインピーダンスアンプ10の入力に接続される差動回路18であって、差動回路18の電流源Is5が入力電流の平均値I2に基づいて制御される差動回路18と、を備えることを特徴とする。

(もっと読む)

パワーアンプのスピーカ接続検査方法及び装置

【課題】昇圧電源を備えたパワーアンプの接続検査に際して、パワーアンプの中点電位とスピーカ接続端子電圧とを比較し、スピーカ接続端子電位が中点電位よりも低い時に接地側にショートしていると判別すると、中点電位がバッテリ電圧より高い時には間違った検査を行う問題点を解決する「パワーアンプのスピーカ接続検査方法及び装置」とする。

【解決手段】パワーアンプの昇圧電源に、バッテリ電圧を昇圧する昇圧手段と並列にバッテリ電圧を引き込むバッテリ電圧引込手段とを設けると共に、昇圧電源からパワーアンプICへの供給電圧を前記昇圧手段とバッテリ電圧引込手段とを切り替える切替手段とを設ける。スピーカ接続検査を行う時には、切替手段によりパワーアンプICへの電圧をバッテリ電圧側に切り替え、接続検査時にはバッテリ電圧の中点電位を用いて、その中点電位よりも端子電圧が低い時のみ接地側ショートと判別する。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

電力増幅装置、電力増幅装置の入力バイアス電圧調整方法

【課題】入力バイアス電圧の調整の時間的効率を大幅に向上することができる電力増幅装置および電力増幅装置の入力バイアス電圧調整方法を提供すること。

【解決手段】バイアス電圧供給部は、GaN−FETのゲートにバイアス電圧を与える。演算制御部は、異なる時点の負荷電流の差を算出する。参照テーブルは、GaN−FETに対応して定められている、ゲートソース間電圧を一定に保ち始めたときからドレイン電流が変化していく当初のドレイン電流変化率と、ゲートソース間電圧を一定に保ち始めたときのドレイン電流を時間経過後に保つため必要なゲートソース間電圧の変更量との対応関係を記述している。参照制御部は、負荷電流の差を参照テーブルのドレイン電流変化率に当てはめて、ゲートソース間電圧の変更量を取り出す。バイアス電圧変更制御部は、変更量に基づいて、ゲートバイアス電圧を変更するように、バイアス電圧供給部を制御する。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】変調信号のオンデューティー比が上限付近の状態が継続しても、D級増幅器を正

常に動作させて駆動信号を出力が可能とする。

【解決手段】駆動波形信号から生成した変調信号を電力増幅した後、平滑化することによ

って駆動信号を生成する。変調信号を電力増幅するデジタル電力増幅器では、電源とグラ

ンドとの間で2つのNチャンネル(以下ch)MOSFETをプッシュ・プル接続し、更

に、電源側のNchMOSFETに対して並列にPchMOSFETを接続する。こうす

れば、電源側のNchMOSFETをONにするためのブートストラップコンデンサーに

蓄えられた電荷が不足してNchMOSFETをONにすることができない場合でも、P

chMOSFETをONにすることで電力増幅を行うことができ、駆動信号を出力するこ

とが可能となる。

(もっと読む)

光信号検出装置、浮遊微粒子検出装置および火災警報装置

【課題】端子構造の複雑化を回避しつつ、ノイズの影響を抑制できる光信号検出装置、浮遊微粒子検出装置および火災警報装置を提供する。

【解決手段】この光信号検出装置21によれば、光信号検出デバイス14がフォトダイオード101の受光信号を増幅する電流増幅回路102を有するので、微小信号を扱うフォトダイオード101の出力ラインは光信号検出デバイス14内に収まり、出力ラインを短くすることが可能となり入力ノイズの影響を低減できる。また、電流増幅回路102でフォトダイオード101の受光信号を増幅する分だけ、アンプ兼増幅抽出デバイス17のゲインを抑制でき、入力ノイズの影響を低減できる。また、光信号検出デバイス14は、電流増幅回路102が増幅した信号を出力する信号出力端子103が電流増幅回路102を駆動する直流電流を供給するための端子を兼ねているので、2端子デバイスとすることができる。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

カレントミラー回路及びそれを有する増幅回路

【課題】電源電圧の変動に対する出力電流の変動が小さいカレントミラー回路を提供すること。

【解決手段】カレントミラー回路5は,トランジスタM12の第2のドレイン電流を第2の比率で複製した第2の複製電流を生成する第2の複製電流生成回路J2と,基準電流と第2の複製電流が流入する接続ノード接続ノードQ1とグランドとの間に設けられ,トランジスタM11の第1のドレイン電流を第1の比率で複製した第1の複製電流を生成する第1の複製電流生成回路J1とを有し,出力トランジスタM10のゲートとトランジスタM11,M12のゲートと接続ノードQ1とが接続されている。

(もっと読む)

ベース電流補償回路

【課題】印加電圧が変動しても、入力端子から流れ込む電流を一定とすることのできるベース電流補償回路を提供する。

【解決手段】実施形態のベース電流補償回路1は、補償対象トランジスタQ10のベースが接続される入力端子INにベースが接続されたアーリー効果相殺用トランジスタQ2が、補償対象トランジスタQ10に発生するアーリー効果と同じアーリー効果を補償電流生成用トランジスタQ1に発生させる。補償電流生成用トランジスタQ1に流れる電流は、カレントミラー回路11で折り返されて、補償対象トランジスタ10のゲートへ注入される。

(もっと読む)

バイアス制御回路

【課題】増幅器の歪み特性を緩和しつつ、低レベル高周波信号に対する利得低下を抑制する。

【解決手段】高周波信号を増幅する増幅器(20)のバイアスを制御するためのバイアス制御回路(10)は、高周波信号の包絡線を検波する検波器(11)と、増幅器(20)に一定のバイアス電流を供給する第一のバイアス回路(12)と、高周波信号の包絡線のレベル変動に追従して変動するバイアス電流を増幅器に供給する第二のバイアス回路(14)とを備える。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

定電流回路

【課題】 電流値のバラツキの小さい定電流回路を提供する。

【解決手段】 Pチャネルトランジスタ3および9は、互いに比例した定電流を出力する第1および第2の定電流源として機能する。キャパシタ5は、Pチャネルトランジスタ3に直列接続されている。放電用スイッチであるNチャネルトランジスタ6は、周期的にキャパシタ5の充電電荷を放電させる。コンパレータ7は、キャパシタ5の充電電圧V1が基準電圧Va以内である期間だけPチャネルトランジスタ4および10をONにすることにより第1および第2の定電流源による電流の出力を行わせる。キャパシタ11、抵抗12およびキャパシタ13からなる平滑化回路19は、第2の定電流源の出力電流を平滑化する。Nチャネルトランジスタ14および15からなる出力用カレントミラーは、この平滑化回路19により平滑化された電流に比例した電流を出力する。

(もっと読む)

21 - 40 / 565

[ Back to top ]