Fターム[5J500AM13]の内容

増幅器一般 (93,357) | 接続及び構成 (5,069) | フィードバック(帰還)構成 (1,498) | 負帰還(単なるエミッタ帰還抵抗を除く) (832)

Fターム[5J500AM13]に分類される特許

21 - 40 / 832

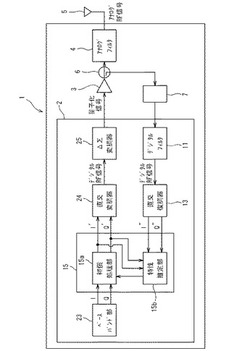

増幅装置、デジタル信号処理装置、及び無線通信装置

【課題】増幅器の出力を複雑なアナログ信号処理を行うことなく取得できるようにする。

【解決手段】 増幅装置1は、増幅器3と、増幅器3によって増幅されるべき信号を出力するデジタル信号処理部2と、増幅器3の出力側に設けられたアナログフィルタ4と、を備えている。デジタル信号処理部2は、増幅器3の出力に基づいて、増幅器3の歪補償を行う歪補償部15と、増幅器3によって増幅されるべき信号に対してΔΣ変調を行って量子化信号を出力するΔΣ変調部25と、を備えている。増幅器3は、量子化信号を増幅し、前記アナログフィルタ4は、量子化信号からアナログ信号を生成する。デジタル信号処理部2は、歪補償部15による歪補償のために、増幅器3から出力された量子化信号を取得する。

(もっと読む)

増幅装置

【課題】 入力電圧が低く、特性を向上させた増幅装置を提供する。

【解決手段】 増幅装置は、一対の受光素子からそれぞれ入力された第1及び第2の電流信号In(+),In(−)を、第1及び第2の電圧信号Vo(−),Vo(+)にそれぞれ変換して出力する第1及び第2のトランスインピーダンスアンプ20と、第1及び第2の電流信号In(+),In(−)の各電流を分流する分流回路24と、第1及び第2の電圧信号Vo(−),Vo(+)の平均電圧値を示す平均信号を生成して出力する平均値検出回路と、平均信号Vav、及び第1及び第2の電圧信号Vo(−),Vo(+)のオフセット電圧値に基づいて、分流回路24に分流される第1及び第2の電流信号In(+),In(−)の各電流値を制御する制御回路23とを含む。

(もっと読む)

高周波増幅回路および無線通信装置

【課題】低負荷の素子を駆動可能にすることで出力インピーダンスを低く抑えることが可能な増幅回路を提供する。

【解決手段】入力信号を増幅するn段構成の増幅回路と、n段目の前記増幅回路と(n+1)段目の前記増幅回路との間に設けられる(n−1)個のインピーダンス変換器と、を備え、前記(n−1)個のインピーダンス変換器は、前記増幅回路間の電力反射を抑制できるインピーダンス変換を行うことを特徴とする、増幅回路が提供される。かかる構成により、増幅回路は、低負荷の素子を駆動可能にすることで出力インピーダンスを低く抑えることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

歪補償装置および歪補償方法

【課題】歪補償の精度を向上させる。

【解決手段】歪補償装置10は、増幅器で生じる信号の歪みを補償する。記憶部11は、歪補償に用いられる複数の補償係数を記憶する。選択部12は、信号の電力レベルを示す指標値に対応する補償係数を複数の補償係数の中から選択する。選択部12は、電力レベルが閾値を超えるか否か判定し、判定結果に応じて、対数演算を用いずに算出される第1の指標値または対数演算を用いて算出される第2の指標値を使用する。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、電極端における電界集中を緩和してデバイス特性の劣化を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を提供する。

【解決手段】HEMTは、SiC基板1上に、化合物半導体層2と、開口6bを有し、化合物半導体層2上を覆う、窒化珪素(SiN)の保護膜6と、開口6bを埋め込むように化合物半導体層2上に形成されたゲート電極7とを有しており、保護膜6は、その下層部分6aが開口6bの側面から張り出した張出部6cが形成されている。

(もっと読む)

電圧電流変換回路および電圧制御発振回路

【課題】入力電圧に正確に対応した値の出力電流を得ることができる電圧電流変換回路およびその電圧電流変換回路で生成した電流を用いて高精度な発振周波数を得ることができるようにした電圧制御発振回路を提供する。

【解決手段】3容量Csと、容量CBと、スイッチSW1〜SW4と、オペアンプOP1と、トランジスタM1,M2とを備え、スイッチSW1,SW2がオン/オフするときスイッチSW3,SW4がオフ/オンするようにスイッチSW1〜SW4を制御し、電圧入力端子1に入力した入力電圧Vinに比例した電流IREFをトランジスタM1のドレインから出力する。

(もっと読む)

RFパワーモジュール

【課題】多段増幅段を含むRF電力増幅回路の低パワーおよび中間パワー時における電力付加効率(PAE)の低下を軽減する。

【解決手段】RF電力増幅回路313は、前段増幅器310、後段増幅器311、制御部312を具備する。前段増幅器310はRF送信入力信号Pinに応答して、前段増幅器310の出力の増幅信号に後段増幅器311が応答する。制御部312は、出力電力制御電圧Vapcに応答して、前段増幅器310と前記後段増幅器311のアイドリング電流を制御して前段増幅器310と前記後段増幅器311の利得を制御する。出力電力制御電圧Vapcに応答して、前段増幅器310のアイドリング電流と利得とは第1の連続関数2ndAmpに従って連続的に変化して、後段増幅器311のアイドリング電流と利得とは第2の連続関数3rdAmpに従って連続的に変化する。第2の連続関数3rdAmpは、第1の連続関数2ndAmpよりも1次以上高次の関数である。

(もっと読む)

増幅回路および帰還回路

【課題】反転入力容量Csinが異なる場合、帰還容量Cfが小容量の固定値であっても、周波数特性の肩特性の劣化やピークがほとんど生じない増幅回路および帰還回路を提供する。

【解決手段】個別に負帰還をかけるとともに直列に接続された複数の増幅器と、前記複数の増幅器に含まれる出力側の増幅器の出力側と入力側の増幅器の入力側に接続された帰還手段(帰還回路)とを備え、前記複数の増幅器は奇数個の反転増幅器を含む構成である。

(もっと読む)

受信回路

【課題】正の単一電源で作動(動作)するオペアンプを用いて負の信号レベルの信号を含む受信信号を増幅することのできる受信回路を提供する。

【解決手段】受信回路100は、基準端子11と基準端子11の電圧を基準とする受信信号を出力する信号端子12とを有する信号部10と、正の入力端子21と負の入力端子22と出力端子23とを有し、正の単一電源E2から電圧が印加されて作動するオペアンプ20と、出力端子23と負の入力端子22との間に接続される第1負荷部30と、信号端子12と負の入力端子22との間に接続される第2負荷部40と、カソード側が接地され、アノード側が基準端子11と正の入力端子21とに接続されるダイオード52を含む基準電圧部50と、を備える。

(もっと読む)

送信装置及びこの送信装置で使用される制御方法

【課題】EXCITERユニットの簡素化、コスト削減の実現を可能にする。

【解決手段】送信装置は、電力増幅部13と、送出部15と、冷却部27と、温度検出手段181と、出力電力検出手段182と、冷却制御手段183とを備えている。電力増幅部13は、伝送信号を電力増幅する。送出部15は、電力増幅部13の出力を伝送路へ送出する。冷却部17は、電力増幅部13を冷却する。温度検出手段181は、電力増幅部13の温度を検出する。出力電力検出手段182は、電力増幅部13の出力電力を検出する。冷却制御手段183は、温度検出手段181の検出結果及び出力電力検出手段182の検出結果に基づいて、冷却部17の冷却処理を制御する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

増幅器における可変フィードバック

【課題】線形性の改善されたノイズ指数および低ノイズ増幅器を提供する。

【解決手段】受信信号強度インジケータ201の出力に基づく可変ネガティブフィードバック203を含む増幅器M1が開示されている。フィードバックは、高受信信号レベルについて増加され、低受信信号レベルについて減少されるとしてもよい。実施形態において、可変フィードバック203は、複数の離散的なインピーダンス設定を含むとしてもよい。振幅および/または時間ヒステリシスは、組み込まれていてもよい。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

駆動回路並びに関連するエラー検出回路及び方法

【課題】

発光装置のための低出力電圧駆動回路が、本発明の例示としての実施形態に従って提供される。

【解決手段】

また、オフセット電圧キャンセル及び/又はレベルシフタが、駆動電流の精度を高くするように駆動回路に組み込まれる。更に、エラー検出回路及び方法は、本発明の駆動回路の最小の出力電圧を検出して対応できるように、用いられる。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

電力増幅器のバイアス回路および電力増幅器

【課題】コンプリメンタリSEPP回路において、出力抵抗を高くすることなくバイアス電流の安定したバイアス回路を提供する。

【解決手段】バイアス電流を検出する差動増幅器と、所定の電圧値と差動増幅器の出力電圧値との差分を増幅する演算増幅器と、演算増幅器の出力信号を絶縁伝達する絶縁伝達器と、絶縁伝達器の出力に応じたバイアス電圧を出力するバイアス電圧源とを備えたコンプリメンタリSEPP回路のバイアス回路。差動増幅器、演算増幅器、絶縁伝達器の動作により、バイアス電圧源は、バイアス電流が増加すると出力するバイアス電圧を低下させる。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

21 - 40 / 832

[ Back to top ]