国際特許分類[G01R31/28]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767)

国際特許分類[G01R31/28]の下位に属する分類

限界試験,例.供給電圧を変えることによるもの (114)

非接触試験 (272)

アナログ回路の試験 (200)

アナログデジタル混在回路の試験

デジタル回路の試験 (638)

国際特許分類[G01R31/28]に分類される特許

21 - 30 / 4,543

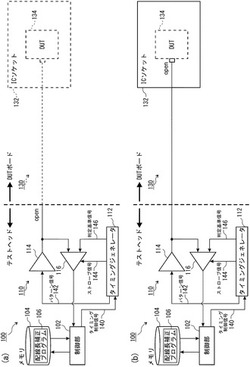

ICテスタ用信号遅延測定プログラムおよびその測定方法

【課題】 TDR測定によって、DUTボードの配線長に依存した信号遅延時間を正確に求めることが可能なICテスタ用信号遅延測定プログラムを提供する。

【解決手段】 本発明にかかるICテスタ用信号遅延測定プログラム106の構成は、コンピュータを、テストヘッド110側からステップ波形148を印加してその入射波と反射波との第1到達時間差Td1、第2到達時間差Td2を測定するTDR測定手段、第1スルーレートS2、第2スルーレートS2を演算するスルーレート演算手段、第1スルーレートS2と第2スルーレートS2とを用いて第2到達時間差Td2を補正し、第1到達時間差Td1を差し引くことで信号遅延時間を演算する信号遅延演算手段、として機能させることを特徴とする。

(もっと読む)

基板検査治具、治具ベースユニット及び基板検査装置

【課題】検査対象の被検査基板の構成の変更に伴う基板検査治具の構成の変更の負担を軽減できる基板検査治具及びその関連技術を提供する。

【解決手段】この基板検査治具2は、治具本体6、電極ユニット7及び検査ヘッド8を備える。電極ユニット7は、略マトリクス状に配設された複数の電極ヘッド部を有し、治具本体6に交換可能に取り付けられる。検査ヘッド8は、複数のプローブと、プローブ保持部材とを有し、その各プローブの後端部が電極ユニット7のいずれかの電極ヘッド部と電気的に接触するように、電極ユニット7又は治具本体6に交換可能に取り付けられる。電極ユニット7の電極ヘッド部は、プローブの配置形態の異なる複数種類の検査ヘッド8に対応可能なように、検査ヘッド8のプローブの配設ピッチよりも小さな配設ピッチで略マトリクス状に配設されている。

(もっと読む)

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

DC−ACプローブ・カード

【課題】被測定AC信号の損失と反射を低減する。

【解決手段】DC−ACプローブ・カード20は、プローブ・ニードル26及び31を有し、これらは、DUTに接触する末端を夫々有する。接続経路24及び30は、試験計装22及び28をプローブ・ニードル26及び31に接続するよう使用できる。接続経路24及び30の夫々は、夫々の対応する試験計装22及び28と、プローブ・ニードル26及び31の間に、AC測定に適した所望特性インピーダンスと、DC測定に適したガードされた経路の両方を提供する。

(もっと読む)

試験信号仲介基板

【課題】 伝搬遅延時間の測定値が所定範囲外になる恐れがある配線が、外部のLSIテスタによって測定対象となっても、LSIテスタにエラー処理を実行させないようにできるプローブカードを提供する。

【解決手段】 プローブカードの少なくとも一部の配線はそれぞれ、自配線の一端に、投入された伝搬遅延時間測定用のパルス波形を、自配線の他端以外の箇所で反射させる反射箇所規定構造を有する。例えば、反射箇所規定構造を有する配線は、LSIテスタ寄りの配線部分と、DUT寄りの配線部分と、これらの配線部分間に介挿された、パルス波形の周波数成分に対し、各配線部分より高インピーダンスのフェライトビーズとを有し、LSIテスタ寄りの配線部分とフェライトビーズとの境界をパルス波形の反射箇所にしている。

(もっと読む)

21 - 30 / 4,543

[ Back to top ]