国際特許分類[G01R31/28]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767)

国際特許分類[G01R31/28]の下位に属する分類

限界試験,例.供給電圧を変えることによるもの (114)

非接触試験 (272)

アナログ回路の試験 (200)

アナログデジタル混在回路の試験

デジタル回路の試験 (638)

国際特許分類[G01R31/28]に分類される特許

51 - 60 / 4,543

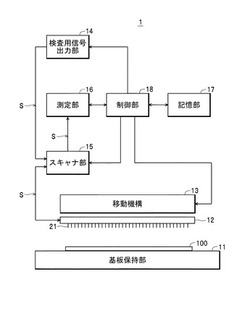

回路基板検査装置および回路基板検査方法

【課題】検査効率を向上させる。

【解決手段】導体パターンを有する基板に電子部品が搭載された回路基板100における複数の接触点に対してプロービングされたプローブ21を介して入出力する電気信号Sに基づいて電子部品の良否を判定する検査処理を実行すると共に、検査処理において電子部品が不良と判定したときにはプロービングの再実行後に検査処理を再実行する制御部18を備え、制御部18は、検査処理を再実行する際に、直前の検査処理において不良と判定したときの不良の内容が予め決められた特定の内容に該当する電子部品だけを対象として電子部品の良否を判定する。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

移動体通信装置試験システムおよび試験方法

【課題】試験対象に対してシーケンス測定を実行する際に、取得データ量の面で、誤った測定の無駄な測定をしないで済むようにする。

【解決手段】シーケンス測定制御手段35が実行指定された測定シーケンスにしたがう制御を開始する前に、実行指定された測定シーケンスで送受信部21が解析対象として取得する予定のデータ量の合計値を算出するデータ量算出手段40と、算出したデータ量の合計値が受信データメモリ23の所定容量に応じて予め設定した許容値を超えるか否かを判定するデータ量判定手段41とを備え、シーケンス測定制御手段35は、データ量判定手段41により算出したデータ量の合計値が許容値を超えると判定されたとき、その判定結果を表示部61に表示して、ユーザーに通知する。

(もっと読む)

マルチチップ積層体の製造方法

【課題】 本発明の目的は、無基板チップ積層体の導通検査を従来の検査装置で実施可能なTSV実装プロセスを用いて製造するマルチチップ積層体の製造方法を提供する。

【解決手段】 ウエハを分割して形成したチップ110の表面に複数のテスト電極130と複数の外部電極131とを形成する。チップ110には外部電極131とテスト電極130とを導通する複数のシリコン貫通孔111が設けられる。次に、無基板チップ積層体100を接着テープ252の上に固定し、充填封止体150を接着テープ252上に形成する。次に、ウエハテストトレー260内に接着テープ252を支持するテープキャリア250を固定する。導通検査では、無基板チップ積層体100は接着テープ252に接着されたままウエハ検査装置270内に搭載され、ウエハ検査装置270の複数のプローブ271によって無基板チップ積層体100の導通の良否を判定する。

(もっと読む)

差動伝送半導体装置

【課題】正確な性能測定を容易にした差動伝送半導体装置を提供する。

【解決手段】差動対入力信号に応答してステップ信号を各々が生成する複数の入力コンパレータと、当該ステップ信号を伝送する伝送回路と、当該伝送回路によって伝送されたステップ信号に応答して差動対出力信号を各々が生成する複数の出力アンプと、を含み、供給されるテスト指令に応じて当該出力アンプの差動対出力信号を択一的に取り込んで、これに含まれるクロスポイントの発生タイミングを示す検査出力信号を生成する。

(もっと読む)

配線板、配線板の検査方法

【課題】絶縁板の主面または内部に実装された電子部品の接続検査を簡明化すること。

【解決手段】第1の電子部品が有する第1の電源端子に接続がされるための第1のランドパターンと、第2の電子部品が有する第2の電源端子に接続がされるための第2のランドパターンと、第1の電源端子を除くいずれかの端子に接続がされるための第3のランドパターンを含み、かつ第2の電源端子を除くいずれかの端子に接続がされるための第4のランドパターンを含み、かつ第3のランドパターンと第4のランドパターンとを電気的に接続するように絶縁板に設けられた配線部と、第1のランドパターンに電気的に接続して設けられた、少なくとも一部が主面上に存在する第1の電源リード部と、第2のランドパターンに電気的に接続して設けられた、少なくとも一部が前記主面上に存在し、かつ、第1の電源リード部とは電気的に分離して存在する第2の電源リード部とを具備する。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】複数の被試験デバイスに対して電源供給部から電源の供給を行って試験を行うときに、同時スイッチングノイズの影響を抑制することを目的とする。

【解決手段】本発明の半導体試験装置1は、複数のDUT3に電源を供給するデバイスパワーサプライ5を備える半導体試験装置1であって、DUT3の試験を行うピンエレクトロニクスカード2のドライバ12およびコンパレータ13とDUT3との間の伝送経路15の伝播遅延Tpdを校正するデータをタイミング校正データとして記憶するタイミング校正データ記憶部21と、DUT3を複数のグループに分割して、当該グループごとに異なる遅延量をタイミング校正データに加算する遅延量加算部25と、を備えたことを特徴としている。

(もっと読む)

任意波形発生装置のチャンネル校正方法

【課題】任意波形発生装置の校正方法を改善する。

【解決手段】Sパラメータを用いて任意波形発生装置を校正する。任意波形発生装置が有するチャンネルとしては、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルでも良い。差動信号を生成する場合でも良く、2チャンネルを1対として、複数のチャンネル対を校正できる。このとき、各チャンネルは、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルで1つのチャンネルを構成する場合でも良い。

(もっと読む)

51 - 60 / 4,543

[ Back to top ]