国際特許分類[G01R31/28]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767)

国際特許分類[G01R31/28]の下位に属する分類

限界試験,例.供給電圧を変えることによるもの (114)

非接触試験 (272)

アナログ回路の試験 (200)

アナログデジタル混在回路の試験

デジタル回路の試験 (638)

国際特許分類[G01R31/28]に分類される特許

31 - 40 / 4,543

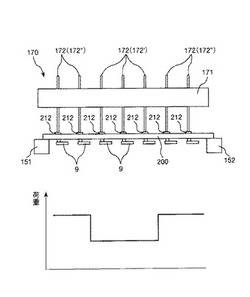

検査方法および検査装置

【課題】本発明の目的は、支持基板の破損を防止するとともに、支持基板とプローブヘッドが有するプローブピンとを確実に接触させ、信頼性に優れる検査を行うことのできる検査方法および検査装置を提供すること。

【解決手段】複数の振動子9を支持する支持基板200にプローブピン172を押し当て、振動子9の特性を検査する検査方法であって、支持基板200の撓みの度合いを検出する検出工程と、検出工程で検出した支持基板200の撓みの度合いに応じて、複数のプローブピン172によって支持基板200に加えられる荷重の分布を設定する荷重設定工程と、複数のプローブピン172を備えているプローブヘッド170を準備する準備工程と、を含んでいる。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

再構築したメモリ空間の回収方法

【課題】廃棄されたダイから使用可能なメモリ空間を回収するメモリ容量を有するメモリを回収する方法を提供する。

【解決手段】再構築したメモリ空間の回収方法は、廃棄されたダイを回収し、使用可能なメモリ空間に応用し、規格化又は非規格化のメモリ容量を有するメモリを形成する。再構築したメモリ空間の回収方法は、ブロックエリア、ページエリア及びセルエリアを有するダイを準備するステップと、ダイのブロックエリア、ページエリア及びセルエリアのうちの1つを走査し、ダイに対応したエリア中にテストデータを書き入れ、ダイによりテストデータの読み書き及び比較を行ってテスト結果を得て、このテスト結果に基づき、正常及び異常なブロックエリア、ページエリア又はセルエリアを標記するステップとを含む。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

スキャンチェーン検査装置及び検査方法

【課題】 スキャンチェーンの検査を好適に行うことが可能なスキャンチェーン検査装置及び検査方法を提供する。

【解決手段】 半導体装置10のスキャンチェーンに検査信号を供給する検査信号供給部18と、スキャンチェーンの各レジスタでの検査信号の信号レベルの時間変化を測定するレジスタ測定部20と、測定部20による測定結果に基づいて各レジスタにレジスタ番号を付与するレジスタ番号解析部51を有する検査解析装置50とによってスキャンチェーン検査装置1Aを構成する。供給部18は、信号長nが異なるm種類の検査信号列を供給する。解析部51は、信号長nの検査信号列を用いた測定結果からスキャンチェーンの複数のレジスタをn個のグループに分けるグループ分けをm種類の検査信号列のそれぞれについて行い、その結果に基づいて各レジスタにレジスタ番号を付与する。

(もっと読む)

試験装置

【課題】電源電圧変動を制御可能な試験装置を提供する。

【解決手段】試験装置2は、被試験デバイス(DUT)1を試験する。メイン電源10は、DUT1の電源端子P1に供給すべき電力信号VDDを生成する。メイン電源10の出力端子P4とDUT1の電源端子P1の間の電源ライン上には、可変電源経路部30が設けられる。可変電源経路部30は、その電気的特性が可変に構成される。制御部32は、可変電源経路部30の電気的特性を制御する。

(もっと読む)

半導体集積回路の検査方法および半導体集積回路

【課題】半導体集積回路のクロックに一定周波数のクロックのみを供給しつつ半導体集積回路の内部クロックを動的に変化させて半導体集積回路のランダム・ロジックを検査する。

【解決手段】複数の組み合わせ回路と当該複数の組み合わせ回路のスキャンテストを行うためのスキャンチェーンを構成する複数のスキャンフリップフロップとを有する半導体集積回路、の検査方法を、クロック生成装置から前記半導体集積回路に一定周波数の第1クロックを入力する入力工程と、前記半導体集積回路の内蔵する分周器が前記第1クロックを分周して第2クロックを生成する分周工程と、前記複数のスキャンフリップフロップに入力するクロックを、前記第1クロックと前記第2クロックとの間で動的に切り替えつつ前記半導体集積回路を検査する検査工程と、により構成する。

(もっと読む)

電源装置およびそれを用いた試験システム

【課題】電源電圧の変動を抑制する。

【解決手段】メイン電源は、DUT1の電源端子P1の電位を所定の目標値に近づくように帰還制御する。制御端子PCNTには、補償電源が生成すべき補償電流の目標波形REFを指示する電流制御信号SCNTが入力される。電流検出回路22は、インダクタL1に流れる電流ILに応じた検出信号VCSを生成する。パルス変調器24は、検出信号VCSを電流制御信号SCNTに応じた目標波形REFと比較し、比較結果に応じてレベルが変化するパルス信号Spを生成する。ドライバ26は、パルス信号Spにもとづいて、第1スイッチSW1および第2スイッチSW2を相補的にスイッチングする。

(もっと読む)

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

半導体装置

【課題】 多様な方式でスキャンテスト経路を形成することができる半導体装置を提供する。

【解決手段】第1チップおよび第2チップを電気的に連結する第1貫通ビアおよび第2貫通ビアと、前記第1チップに配置され、テストデータを受信するとともに前記第1貫通ビアと接続される第1回路部と、前記第1チップに配置され、前記第2貫通ビアおよび前記第1回路部と接続される第2回路部と、前記第2チップに配置され、前記第1貫通ビアと接続される第3回路部と、を含み、前記第1回路部は第1制御信号に応答して前記第1貫通ビアおよび前記第2回路部のうちいずれか一つに前記第1回路の出力信号を出力する。

(もっと読む)

31 - 40 / 4,543

[ Back to top ]