国際特許分類[G01R31/28]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767)

国際特許分類[G01R31/28]の下位に属する分類

限界試験,例.供給電圧を変えることによるもの (114)

非接触試験 (272)

アナログ回路の試験 (200)

アナログデジタル混在回路の試験

デジタル回路の試験 (638)

国際特許分類[G01R31/28]に分類される特許

41 - 50 / 4,543

半導体装置

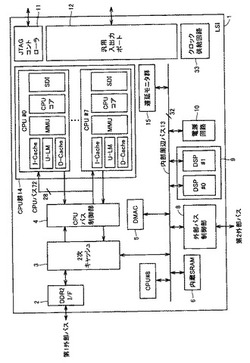

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体チップ、半導体装置、及びその測定方法

【課題】多数の信号用TSVを有する半導体チップを積層した半導体装置では、個々の信号用TSVを導通試験するのに、膨大な工数がかかっていた。

【解決手段】信号用TSVを直接導通試験するのではなく、信号用TSVに隣接した位置にダミーバンプを配列すると共に、複数の半導体チップ間のダミーバンプを一筆書きで描けるような導通経路で、各半導体チップのダミーバンプを接続する。

導通経路の導通試験により、積層された2つの半導体チップの接合面における接合不良を測定、検出できる。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

スイッチングマトリクスおよびその半導体素子の特性試験システム

【課題】スイッチングマトリクスのオン・オフ操作を制御するためにセンサおよびコントローラを備えたスイッチングマトリクスを提供する。

【解決手段】スイッチングマトリクスは、スイッチアレイ30を備えており、スイッチアレイ30は、一つ以上の入力ポートと、一つ以上の出力ポートと、前記入力ポートと前記出力ポートとの間の電気的な通路を開閉するように配置されている一つ以上のスイッチ素子36と、前記電気的な通路の所定の電気的特性を測定するとともに、これに基づいて信号を生成するように配置されている電気的なセンサ38または電気的なセンサアセンブリと、を備えている。電気的なセンサアセンブリが、電圧センサ、電流センサ、または電力センサであることが好ましい。

(もっと読む)

擬似障害発生方法と装置

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法、および、プログラム

【課題】半導体集積回路において、スキャンテスト時における消費電力を削減する。

【解決手段】半導体集積回路設計装置は、第1のスキャンFFのデータ入力端子に接続された第1のロジックコーンの入力端子数である第1の入力端子数と、第1のロジックコーンにデータを設定する第2のスキャンFFのデータ入力端子に接続された第2のロジックコーンの入力端子数である第2の入力端子数とを比較するデザイン解析部と、複数のスキャンFFのそれぞれのデータ入力端子に接続されたロジックコーンの入力端子数、および、複数のスキャンFFのそれぞれを第1のスキャンFFとした場合の前記比較結果に応じて、複数のスキャンFFを複数のグループに分類し、複数のグループのそれぞれに含まれるスキャンFFを相互に接続したスキャンチェーンを複数のグループのそれぞれについて生成するスキャンチェーン構築部と、を備える。

(もっと読む)

41 - 50 / 4,543

[ Back to top ]