国際特許分類[H02M1/00]の内容

電気 (1,674,590) | 電力の発電,変換,配電 (135,566) | 交流−交流,交流−直流または直流−直流変換装置,および主要な,または類似の電力供給システムと共に使用するための装置:直流または交流入力−サージ出力変換;そのための制御または調整 (22,926) | 変換装置の細部[1,2007.01] (2,099)

国際特許分類[H02M1/00]の下位に属する分類

静止型変換器に用いられる放電管の格子制御またはイグナイタ制御電力の発生に用いられる回路

ガス放電管または等価の半導体装置,例.サイラトロン,サイリスタ,を非導通にするために特に適合した回路 (6)

静止型変換器に用いられる半導体装置の制御電圧の発生に用いられる回路 (988)

異なった種類の供給電力,例.交流または直流,から負荷を運転させるための変換装置に用いられる装置 (23)

交流入力または出力から高調波を減少させるための装置 (169)

直流入力または出力からリップルを減少させるための装置 (69)

回路の開閉時に立ち上がり電流を供給するための装置,例.可飽和リアクトルをもつもの (1)

非静止型変換器の接点機構

自動切断によるもの以外の、変換器を保護するための手段 (29)

変換器を起動または停止するための手段 (4)

スイッチング手段が同時導通することを防止するための手段 (7)

磁気的飽和することを防止する手段

変換器の力率を補正または調節するための回路または装置 (6)

変換器の電磁妨害を補償するための回路または装置 (53)

国際特許分類[H02M1/00]に分類される特許

81 - 90 / 744

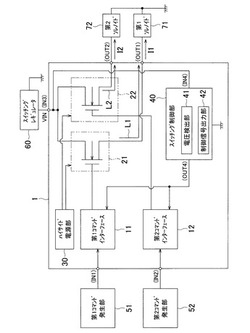

負荷制御装置

【課題】過電流を検出する機能や過電流から出力スイッチング素子を保護する機能を備えた負荷制御装置を提供する。

【解決手段】スイッチングレギュレータ60から電力が供給されて少なくとも一つの負荷71、72に供給する出力電流I1、I2を制御する負荷制御装置1で、負荷に接続されて出力制御信号に応じて負荷に出力電流を供給するときに導通する出力スイッチング素子21、22と、出力電流が過電流であることに起因してスイッチングレギュレータの出力電圧値が所定電圧値を下回ったことを検出したとき、所定時間に亘り出力スイッチング素子を非通電状態に制御する出力スイッチング素子制御手段11、12、40とを備える。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

電力デバイスを試験するための方法および装置

【課題】全出力コンバータ・アセンブリを試験するための方法および装置を提供する。

【解決手段】

全出力コンバータ・アセンブリ(102)に対する試験装置(200/300/400/500)は、公共送電網電力供給装置(202/204)を備えている。試験装置はまた、公共送電網電力供給装置に結合された直流(DC)発生装置(210/214)を備えている。試験装置はさらに、DC発生装置に結合された電力送電網シミュレーション・デバイス(218/224)を備えている。試験装置はまた、電力送電網シミュレーション・デバイスに結合された全出力コンバータ・アセンブリ試験接続部(126/128)を備えている。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

情報処理装置、これを用いたモータ駆動装置、及び、情報処理方法

【課題】 上下アームのスイッチング素子を駆動するとともに、上下アームの異常を検出して異常信号を出力するゲート駆動回路を備える情報処理装置において、異常信号の通知機能が正常であるか否かを判定する。

【解決手段】 情報処理装置(ECU)において、ブートストラップ式のゲート駆動回路は、ゲート駆動の開始前に、通常駆動時ならば先に下アーム駆動信号を出力すべきところ先に上アーム駆動信号D1を出力し(S10)、ダミー異常信号Edを意図的に発生させる(S20)。ここで異常信号通知機能が正常であれば、ダミー異常信号Edは、異常信号出力部から出力され、異常信号線を経由して伝達され、異常信号受信部に受信される。そこで、異常信号受信部がダミー異常信号Edを受信したか否かを確認することで、異常信号通知機能が正常であるか否かを判定する(S30)ことができる。

(もっと読む)

半導体装置

【課題】インバータ回路のサージ電圧を抑制する半導体装置を提供することを課題とする。

【解決手段】スイッチング素子からなる回路S1,S2が封入されたモジュール13,14が、バスバー配線100により、2つ以上並列に接続された回路構成を有するインバータ回路を備えた半導体装置であって、バスバー配線100は、導体層130,140,150と絶縁層110,120とを交互に重ね合わせた、ラミネート構造を有しており、導体層である直流正極130、直流負極140、交流出力150の各配線が、異なる導体層に形成される。

(もっと読む)

短尺対応サージ抑制ユニット

【課題】20m以下の短い電動機駆動用電線長において、サージ電圧抑制効果が低下せず、設置に小さなスペースのサージ抑制ユニットを提供する。

【解決手段】電動機駆動用電線長が短い場合でも、サージ電圧抑制効果を発揮するように、負荷側に駆動線路とサージ抑制線の反射影響を小さくするために並列に接続された整合回路と、前記整合回路と直列に接続されたサージ抑制体とからなり、前記サージ抑制体の終端を高インピーダンスにした構造を持ち、整合回路とサージ抑制体を組合せた。

(もっと読む)

電力変換回路の駆動装置

【課題】フェール信号を出力するフェール用フォトカプラPCfの2次側を直列接続する場合、その配線長が長くなることから、フェール信号のノイズに対する耐性が低下するおそれがあること。

【解決手段】インバータIV1、コンバータCVおよびインバータIV2を構成する上側アームのスイッチング素子と下側アームのスイッチング素子とは、基板30に対して2列に配置され、その制御端子(ケルビンエミッタ電極KE、センス端子ST、ゲートG)が基板30に差し込まれている。これら2列の間には、フェール用フォトカプラPCfが配置されている。インバータIV1に対応するフェール用フォトカプラPCfは、隣接するもの同士で直列接続され、各列の端部が接続されることでU字型の配線構造を有し、その端部がマイコン20に接続されている。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子のオン故障や誤動作によって発生する、スイッチング素子をオフできない異常状態を検出することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aとオフ駆動用FET122aに電流が流れており、かつ、流れている電流の差が所定値以下であるとき、IGBT110dが異常状態にあると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aのオン故障や誤動作によって発生する、IGBT110dをオフできない異常状態を検出することができ、IGBT110aの熱破壊を防止することができる。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流が検出された場合に、ハイサイドスイッチだけでなくハイサイドスイッチに接続される回路を保護することが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ゲート電圧降圧部31は、過電流検出部20からの電流制限信号に応じて、MOSトランジスタ15のゲート電圧を第1の電圧から、第1の電圧と第2の電圧との間の第3の電圧まで、第1の時間変化率で低下させる。これによりMOSトランジスタ15のオン抵抗がMOSトランジスタ15の完全オン時のオン抵抗より高くなる。ゲート電圧降圧部32は、ゲート電圧が第3の電圧に達した後に、ゲート電圧を第3の電圧から第2の電圧まで第2の時間変化率で低下させる。第1の時間変化率は、第2の時間変化率よりも大きい。

(もっと読む)

81 - 90 / 744

[ Back to top ]