Fターム[4M104HH20]の内容

Fターム[4M104HH20]に分類される特許

41 - 60 / 2,580

ダイオードの製造方法

【課題】 空乏層がp型領域からショットキー接続部に広がり易いダイオードの製造方法を提供する。

【解決手段】 半導体基板の一方の表面に形成されているアノード電極と、半導体基板の他方の表面に形成されているカソード電極と、半導体基板内に形成されており、アノード電極に対してオーミック接続されているp型領域と、半導体基板内に形成されており、p型領域に隣接しており、アノード電極に対してショットキー接続されており、カソード電極に対してオーミック接続されているn型領域を有するダイオードの製造方法。この製造方法は、p型不純物をマスクを通して半導体基板に注入する第1注入ステップと、その後に、第1注入ステップと注入深さを変更して前記p型不純物と同種のp型不純物を前記マスクと同一のマスクを通して半導体基板に注入する第2注入ステップとを実行することで、前記p型領域を形成する。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

トレンチ型ショットキー接合型半導体装置及びその製造方法

【課題】 耐圧を低下させることなく、トレンチ開口幅を小さくすることができるショットキー接合型半導体装置を提供する。

【解決手段】 トレンチの断面形状を、トレンチの底面部の中央が高く、周辺が低いサブトレンチ形状とし、p型不純物をドリフト層表面に対して垂直に導入することで、サブトレンチが設けられたトレンチの内壁部に接するように形成されたp+SiC領域が、トレンチの底面の中央での接合位置よりも、トレンチの底面の周辺での接合位置が深くなるように形成する。

(もっと読む)

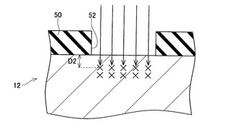

紫外線透過ゲート電極を有する電界効果トランジスタ

【課題】基板の自由度があり、待機時(光非照射時)の電力消費が小さく、また光照射時のS/Nが大きい受光素子を提供することである。

【解決手段】紫外線が透過する材料をFETの電極として用い、また、電子走行領域をAlGaNとGaNとのヘテロ界面等のGaN系膜同士のヘテロ界面とする。

(もっと読む)

基板ホルダー及び真空処理装置

【課題】使用できる温度帯を広げることができる基板ホルダーを提供する。

【解決手段】本発明の基板ホルダー13は、一端部が基板支持面45に導通する接地軸53の他端部に接続され、接地軸53を接地電位に切替えるリレー回路61と、接地軸53の一端部のキャップを基板支持面45に押し付けるように付勢する圧縮コイルばね59と、接地軸53の他端部を真空側に配置し、圧縮コイルばね59の付勢方向に伸縮するベローズ57と、圧縮コイルばね59の付勢方向で狭持されるOリング63とを備えている。この構成により、接地軸53が熱膨張しても基板支持面45との導通を確保できる。

(もっと読む)

半導体装置

【課題】SiCを含む基板を用いたショットキーダイオードのショットキー界面のドリフト層に結晶欠陥が生じている場合に、逆方向漏れ電流の発生を防ぐことで、半導体装置の信頼性を向上させる。

【解決手段】半導体基板上のドリフト層2とショットキー電極4とのショットキー接合部を含むショットキーダイオードにおいて、ドリフト層2の上面に達する結晶欠陥12の上面に、ショットキー電極4を構成する金属に応じて規定される濃度および深さで、アクセプタ不純物を導入してp型半導体領域3を形成し、逆方向漏れ電流の増大を防ぐ。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

窒化物半導体装置の製造方法

【課題】低温の加熱処理によって、コンタクト抵抗の低いオーミック電極を形成することができる方法を提供する。

【解決手段】窒化物半導体層のオーミック電極形成領域に、インジウムあるいはゲルマニウムのような低融点金属7を積層し、低融点金属の融点近傍の低温で加熱処理することにより、窒化物半導体層中に低融点金属が拡散させ、合金層8を形成することによりオーミック接触を形成する。窒化物半導体層表面に残るインジウムあるいはゲルマニウムを除去した後、配線のための金属層9を形成する。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

半導体装置

【課題】高耐圧を確保できながら、逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】その表面12にショットキーメタル22が形成されたエピタキシャル層6を備えるショットキーバリアダイオード1において、エピタキシャル層6の表面12に沿う方向に互いに間隔を空けて配列され、それぞれが表面12から裏面11へ向かってエピタキシャル層6の厚さ方向に延びるp型ピラー層17を形成することにより、エピタキシャル層6にスーパージャンクション構造を形成する。また、エピタキシャル層6の表面12の近傍に、p型ピラー層17よりも不純物濃度の高い電界緩和層19を選択的に形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置の製造方法

【課題】表面電極にめっき層を形成する際に、裏面電極に不必要なめっき層が形成されることによる裏面電極の電気抵抗の影響を抑制しつつ、表面電極にめっき層を欠陥無く形成できる半導体装置の製造方法を提供する。

【解決手段】表面1aに半導体素子の表面電極2が形成され、裏面1bに半導体素子の裏面電極が形成された半導体ウェハ1を用意する工程と、半導体ウェハ1の表面電極2にめっき層3を形成するめっき工程とを有する半導体装置の製造方法において、めっき工程では、表面電極2と半導体ウェハ1の側面1cとを露出した状態とし、かつ、半導体ウェハの裏面1bの全域を被覆した状態として、半導体ウェハ1をめっき液に浸してめっき層を形成する。

(もっと読む)

炭化珪素半導体装置

【課題】ボンディング耐性を向上させた炭化珪素半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、炭化珪素基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に平面視してリング状に形成された低濃度p型JTE領域3と、n型炭化珪素層2の表面近傍の低濃度p型JTE3の内側に該低濃度p型JTE領域3に接触して平面視してリング状に形成された高濃度p型領域4と、高濃度p型領域4上の一部に形成されたp型オーミック電極5と、p型オーミック電極5を覆うと共に高濃度p型領域4上及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

41 - 60 / 2,580

[ Back to top ]