Fターム[4M104HH20]の内容

Fターム[4M104HH20]に分類される特許

101 - 120 / 2,580

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

電子部品用積層配線膜および被覆層形成用スパッタリングターゲット材

【課題】 耐湿性や耐酸化性を改善し、さらに低抵抗な主導電層であるCuと積層した際に、加熱工程を経ても低い電気抵抗値を維持できる、Mo合金からなら被覆層を用いた電子部品用積層配線膜および被覆層を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuを主成分とする主導電層と該導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−x−y−Nix−Tiy、10≦x≦50、3≦y≦30、x+y≦53で表され、残部が不可避的不純物からなる電子部品用積層配線膜。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

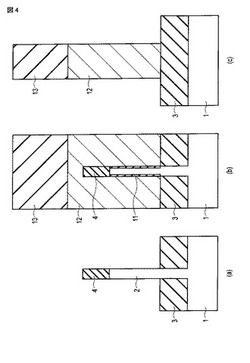

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

導電性膜及びその製造方法並びに導電性膜形成用銀合金スパッタリングターゲット及びその製造方法

【課題】 低抵抗かつ高反射率の特性と共に表面粗さが小さく、高い耐硫化性及び耐塩化性を兼ね備えた導電性膜およびその製造方法を提供すること。

【解決手段】 導電性膜が、Cu:0.1〜2.5原子%、Sb:0.1〜1.5原子%、Ga:0.5〜3原子%を含有し、残部がAgおよび不可避不純物からなる成分組成を有した銀合金で構成されている。この導電性膜は、表面に有機EL素子の透明導電膜が積層され、さらにその上に有機EL層を含む電界発光層が積層される有機EL素子用の反射電極膜として好適である。

(もっと読む)

電子部品用積層配線膜および被覆層形成用スパッタリングターゲット材

【課題】 耐湿性や耐酸化性を改善し、さらに、低抵抗な主導電層であるAlと積層した際に、加熱工程を経ても低い電気抵抗値を維持できる、Mo合金からなる被覆層を用いた電子部品用積層配線膜および被覆層を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Alを主成分とする主導電層と該主導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−x−y−Nix−Tiy、10≦x≦30、3≦y≦20で表され、残部が不可避的不純物からなる電子部品用積層配線膜。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体装置

【課題】窒化ガリウム系半導体で形成された半導体層を有する半導体素子において、消費電力を増大させず、かつ、大型化することなく、半導体素子の電極に電圧をかけたときに発生する電流コラプス現象を抑制する。

【解決手段】窒化ガリウム系半導体が積層されて形成された半導体素子と、半導体素子に対して積層方向に形成され、外部からのエネルギーの入力なしで半導体素子に光を照射する自己発光体とを備える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】リーク電流の少ないダイオードを提供する。

【解決手段】実施形態の半導体装置は、AlXGa1−XN(0<x<1)またはInyAl1−yN(0≦y≦1)からなる第1の半導体層2と、第1の半導体層の同一面上に、ノンドープ、n型又はp型のGaNからなる第1の電子誘起領域1、絶縁膜5とアノード電極7と、第1の電子誘起領域上にカソード電極を備え、第1の電子誘起領域、絶縁膜とアノード電極は第1の半導体層と接合し、絶縁膜は第1の半導体領域とアノード電極の間で、第1の半導体層と接合し、アノード電極と第1の半導体層との接合はオーミック接合であり、カソード電極と第1の電子誘起領域との接合はオーミック接合であることを特徴とする。

(もっと読む)

多元スパッタリング装置

【課題】静電チャックの基板吸着面にパーティクルが付着することを抑制できるようにした多元スパッタリング装置を提供する。

【解決手段】本発明の多元スパッタリング装置SMは、真空チャンバ1と、この真空チャンバの底部に配置され、上面に基板Wを吸着する静電チャック3を有するステージ2と、この真空チャンバの上部に、静電チャックで吸着された基板に対してスパッタ粒子を斜入射させるように配置された少なくとも2個のスパッタリングカソードCと、各スパッタリングカソードと基板との間を選択的に遮蔽する遮蔽手段4とを備える。静電チャックの上面が露出している場合に、当該静電チャックの上面を選択的に覆う保護板5を更に備える。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】 実施形態は、低損失な炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】 実施形態の炭化珪素半導体装置の製造方法は、炭化珪素基板にイオン注入する工程と、前記イオン注入がされた炭化珪素基板に第1の熱処理を行う工程と、前記第1の熱処理がされた炭化珪素基板に前記第1の熱処理より低温の第2の熱処理を行う工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SiC基板上に形成されたデバイスに対して、低温の熱工程にて良好なオーミック特性を備える電極を実現する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、炭化珪素(SiC)で形成されるn型不純物領域上およびp型不純物領域上に金属シリサイド膜を形成し、n型不純物領域上の金属シリサイド膜中にリン(P)をイオン注入し、第1の熱処理を行い、p型不純物領域上の金属シリサイド膜中にアルミニウム(Al)をイオン注入し、第1の熱処理よりも低温の第2の熱処理を行う

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

101 - 120 / 2,580

[ Back to top ]