Fターム[5B046BA04]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049)

Fターム[5B046BA04]の下位に属するFターム

割付、配置、ネスティング (289)

ルート探索、配線 (682)

Fターム[5B046BA04]に分類される特許

21 - 40 / 1,078

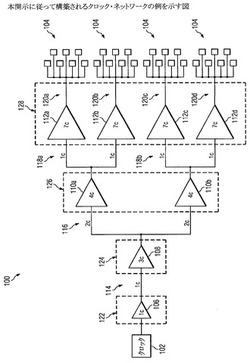

クロック・ネットワーク・メタ合成のためのシステムおよび方法

【課題】クロック到着時間の同時性を保証するクロック分配ネットワークの設計を容易にする。

【解決手段】クロック・ネットワークを構築する方法は、クロック・ネットワークについての設計仕様を受け取る段階を含む。本方法はさらに、前記設計仕様に基づいて前記クロック・ネットワークのトポロジーを決定する段階を含む。本方法はさらに、決定されたトポロジーに基づいて前記クロック・ネットワークについての設計パラメータを決定し、前記設計パラメータを含むクロック・ネットワーク合成ツール仕様ファイルを生成することを含む。本方法はまた、前記仕様ファイルを使って、前記クロック・ネットワークが前記決定されたトポロジーを含み、前記クロック・ネットワークがクロック発生器から前記クロック・ネットワークのエンドポイントまでクロック信号を同期的に分配するよう、前記クロック・ネットワークを合成することを含む。

(もっと読む)

半導体レイアウト設定装置、半導体レイアウト設定方法、及び半導体レイアウト設定プログラム

【課題】チップ面積増大を回避し、適切にリピータバッファを挿入する

【解決手段】レイアウト対象の半導体装置は、第1及び第2の電源ドメインを有し、第2の電源ドメインに属する接続元と接続先を接続する配線を有する。配線禁止許可領域設定部120は、第1の電源ドメイン内に排他的配線禁止領域及び通過配線許可領域を、リピータバッファが駆動可能な最大配線長であるリピータ配線最大長に基づいて設定する。配線設定部130は、排他的配線禁止領域及び通過配線許可領域に基づいて、配線を修正する。リピータ挿入部140は、リピータ配線最大長に応じ、配線に挿入するリピータバッファを設定する。排他的配線禁止領域は、第1の電源ドメイン内で接続する配線は許容し、通過配線を禁止する。通過配線許可領域は、第1の電源ドメインから排他的配線禁止領域を除外した領域であり、通過配線が許容される。

(もっと読む)

プリント基板設計における配線パターン幅の計算方法、配線パターン幅の計算装置、プログラムおよびコンピューター読み取り可能な記録媒体

【課題】配線パターン幅の不足箇所を探す作業や計測する作業などについて目視や設計を繰り返すなどの手間を軽減し、設計障害を発生させることのない配線パターン幅を確保できるか否かを簡便に判断できるようにする。

【解決手段】

プリント基板設計における配線パターン幅の計算方法において、プリント基板におけるパターン上の2つの端子間における領域において、上記2つの端子間を結ぶ配線パターンの幅について、所望の配線パターン幅を確保できるか否かの計算を自動的に行い、上記所望の配線パターン幅を満たす配線パターンの経路を提案するようにした。

(もっと読む)

表示制御装置、その方法及びプログラム並びに回路データ構造

【課題】回路を構成する要素図形の側面情報に、その回路の構造、製造及び/又は検証に関する構成付加情報を関連付けて仮想的に記憶して参照することで、効率的に回路の設計や製造等を行うことができる表示制御装置等を提供する。

【解決手段】3次元回路を構成する要素の構成情報を記憶する回路情報記憶部21と、記憶される構成情報のうち、要素の側面を形成する側面情報に、3次元回路における要素の構造、製造及び/又は検証に関する構成付加情報を関連付けて仮想的に記憶する構成付加情報記憶部22と、回路情報記憶部21及び構成付加情報記憶部22に記憶されている情報に基づいて、3次元回路を表示する表示部24と、表示部24に要素の側面を表示し、その側面の表示に連係して構成付加情報記憶部22に記憶されている構成付加情報を表示する表示制御部23とを備える。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

遅延時間計算プログラム、装置及び方法

【課題】遅延時間計算プログラム、装置及び方法において、回路におけるネットの遅延時間を高精度に計算することを目的とする。

【解決手段】回路内のネットの遅延時間を計算する遅延時間計算処理は、ネットが第1の条件を満たす場合にネットの遅延時間を計算するための第1の遅延計算手順を選択する第1の手順と、第1の手順で第1の遅延計算手順が選択されない場合、第2の条件をネットが満たすか否かに応じて、第1の遅延計算手順及びネットの遅延時間を計算するための第2の遅延計算手順のいずれか一方を選択する第2の手順と、第1の手順或いは第2の手順のいずれかで選択された遅延計算手順によりネットの遅延時間を計算する第3の手順を含むように構成する。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

回路のレイアウト装置,処理方法およびプログラム

【課題】 回路のレイアウト装置で,EOEの発生しやすい箇所を推定することを目的とする。

【解決手段】 回路レイアウト装置1は,被研磨対象となる回路の配線パターンを含む回路情報を取得する回路情報取得部11,回路を任意の単位領域でメッシュ状に区切り,各メッシュ領域について,メッシュ領域の配線密度とメッシュ領域の各辺に隣接する周辺領域の各々における配線密度とを示すメッシュ情報を生成するメッシュ情報生成部12,各メッシュ領域について,メッシュ領域と各周辺領域の密度の関係がEOEの発生条件に該当するメッシュ領域を抽出し,そのエラー情報を生成するエラー抽出部13を備える。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

回路設計支援装置、回路設計支援方法および回路設計支援プログラム

【課題】ペアにするネットのピンの判断を容易にすること。

【解決手段】配線のネットA〜Dを有するピンp1〜p4を複数備える第1のピン群3と、第1のピン群3の各ピンp1〜p4の配線の接続先となりネットA〜Dを有するピンp5〜p8を備える第2のピン群4とが与えられたとき、ペア候補決定部1bは、第1のピン群3および第2のピン群4それぞれにおいて所定距離内にある同じネットA〜Dを有するピンp1〜p4、p5〜p8同士をペア候補に決定する。ペア決定部1cは、ペア候補決定部1bが決定したペア候補を用いて第1のピン群3および第2のピン群4それぞれのピンp1〜p4、p5〜p8のペアを決定する。

(もっと読む)

LSIの回路図復元装置

【課題】レイアウトパターンの任意の一部分の回路図を正確に復元する。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。セル枠決定部600は、条件設定部800内のセル枠決定条件に基づく特定の図形群の外接図形として、表示中のレイアウトパターン上に仮想のセル枠を決定する。端子点決定部500は、このセル枠とセル間配線との交差位置に端子点を決定する。回路復元部700は、条件設定部800内の領域認識条件および素子認識条件に基づき、セル枠内の図形に対して、素子構成領域の認識を行い、認識した各領域と端子点との相互の接続関係に基づいて素子の認識を行い、認識した素子の接続関係を回路図として表示する。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

ノイズ解析装置及びノイズ解析方法

【課題】半導体集積回路で発生するノイズの伝搬を精度よく解析する。

【解決手段】位置特定部2が、解析対象の半導体集積回路のレイアウト情報d1から、高耐圧素子部において、可変容量として設定する、異なる導電型の領域間の接合部の位置を特定し、モデル作成部3が、レイアウト情報d1及び半導体集積回路の製造条件(プロセスパラメータd2)をもとに、ノイズ伝搬路となる配線または基板を、抵抗及び容量を用いてモデル化し、特定された接合部の位置には可変容量を設定する。

(もっと読む)

印刷回路基板用部品配置ツール

【課題】

PCBのレイアウトを作成する方法及びシステムを提供する。

【解決手段】

一実施形態において、印刷回路基板(PCB)のレイアウトが、前記PCB上のn個の位置それぞれにn本の境界線を作成し、且つ前記n本の境界線上それぞれにn組の電子部品を配置することによって作成され、前記PCBに対する一組のレイアウト要求が満足されるまで、前記PCBの前記レイアウトが反復的に調整されて評価される。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

多出力電源回路の設計方法及び多出力電源回路の設計装置

【課題】少ない工数で高効率の電圧コンバータの組み合わせを探索できる多出力電源回路の設計方法及びその設計装置を提供する。

【解決手段】複数の電源ドメインに出力電源を供給する多出力電源回路の設計方法は,入力電源(根)と複数の出力電源(葉)との間に電圧コンバータを有するツリー構造をランダムに生成する工程とそのツリー構造の多出力電源回路の電力効率を計算する工程とを,とりうる全てのツリー構造の数より少ない回数だけ繰り返し,最良の電力効率を有するツリー構造を探索する。さらに,前記探索工程で見つけたツリー構造のうち任意の出力電圧を出力する電圧コンバータ以前の入力側の複数の電圧コンバータを有する入力側ツリー構造について,前記探索工程を再度行い,当該探索で検出されたより良いコスト関数値を有する入力側ツリー構造に置き換える改善を行う。改善工程を任意の出力電圧を順次入力側に移動して繰り返す。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】広範な範囲で遅延値を調整可能なレイアウト装置及びレイアウト方法を提供すること。

【解決手段】本発明にかかるレイアウト装置1は、遅延値算出部12と、バッファ移動部14と、を備える。遅延値算出部12は、上位バッファから出力されるクロック信号を伝搬する複数のクロックパスの遅延値を算出する。バッファ移動部14は、遅延値算出部12により算出された遅延値に基づいて、上位バッファと複数の下位バッファとを接続する複数のクロック信号線が非等長となるように、上位バッファを移動させる。

(もっと読む)

21 - 40 / 1,078

[ Back to top ]