Fターム[5E346HH24]の内容

多層プリント配線板の製造 (97,916) | 目的、課題、効果 (10,213) | 製品性能に関するもの (1,703) | 薄形化 (335)

Fターム[5E346HH24]に分類される特許

61 - 80 / 335

回路実装基板

【課題】電子部品の実装高さを抑えて高密度実装を行うことが可能な回路実装基板を提供する。

【解決手段】回路実装基板10は、凹部18の側壁に側壁接合端子19を形成した電子基板12と、屈曲性を有し表面に外部接合端子29を形成したフレキシブル基板20とを備え、フレキシブル基板20を凸形状に屈曲させた状態で凹部18に挿入して、側壁接合端子19と外部接合端子29とを接合して構成した。これにより、電子部品の実装高さを抑えて高密度実装が可能となる。

(もっと読む)

半導体チップを内蔵するプリント配線板

【課題】層間接着材料による悪影響のない半導体チップを内蔵するプリント配線板およびその製造方法を提供する。

【解決手段】本発明の半導体チップを内蔵するプリント配線板10は、複数の接続パッドが形成される第1基板100と、前記第1基板100の前記複数の接続パッド160上に接続される半導体チップ400と、前記第1基板100と共同して前記半導体チップを覆う金属ケース500と、前記第1基板100に積層された状態では前記金属ケース500の露出面と同じ高さを有し、かつ前記金属ケース500が位置する箇所に切り欠き部が形成される第2基板200,300と有する。そして、前記金属ケース500の露出面を露出して前記第1基板100に第2基板200,300を積層する。

(もっと読む)

カメラモジュール用電気/電子部品埋設基材

【課題】小型化、薄型化及び軽量化を実現することのできる、新規なカメラモジュール用電気/電子部品埋設基材を提供する。

【解決方法】絶縁基材中に埋設された電気/電子部品と、前記絶縁基材の、少なくとも両主面上に設けられ、前記電気/電子部品と電気的機械的に接続された配線パターンと、前記少なくとも両主面上において設けられた配線パターン同士を、直接的又は間接的に、電気的機械的に接続する層間接続体とを具え、前記層間接続体は、前記電気/電子部品が埋設された領域の、前記絶縁基材の平面方向に沿った位置において、前記絶縁基材の一方の主面上に設けられた配線パターン上に設けるべき固体撮像素子の少なくとも一部と重複するように配置され、かつ前記絶縁基材の平面方向に沿った位置において前記絶縁基材に内包されるようにして、カメラモジュール用電気/電子部品埋設基材を構成する。

(もっと読む)

プリント回路板

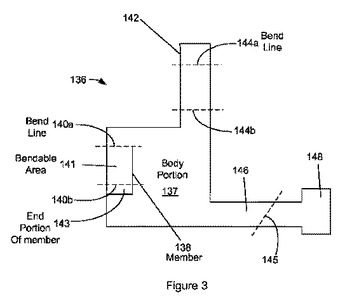

互いに異なるレベル及び姿勢に位置する回路にデバイス・コンポーネントを接続するための方法が記載される。第1回路は多平面リジッド回路板上に位置してもよく、多平面リジッド回路板は、多平面リジッド回路板と共通の基板を共有し、多平面リジッド回路板の基体部から延びる少なくとも1つの可撓性部材を含みうる。可撓性部材は電力及び/又はデータを伝達するために用いられる配線と、電力及び/又はデータ配線に結合されたインタフェースとを含みうる。可撓性部材は多平面リジッド回路板の基体部上の第1回路を別のデバイス・コンポーネントに関連する第2回路に接続するようにそらされ又はねじられうる。  (もっと読む)

(もっと読む)

回路板とその製造方法

【課題】製造工程を減らし、生産品の信頼性を高めることのできる回路基板およびその製造方法を提供する。

【解決手段】2つの金属層102の周縁を接合して、密封エリアを形成する。密封エリアを貫通する少なくとも1つのスルーホールを形成する。2つの絶縁層112を2つの金属層の上に形成する。2つの導電層122を2つの絶縁層の上に形成する。2つの絶縁層および2つの導電層を2つの金属層の上にラミネートして、互いに接合された2つの金属層を2つの絶縁層の中に埋め込み、且つ2つの絶縁層をスルーホール内に充填する。2つの金属層の密封エリアを分離して、それぞれ分離された2つの回路基板を形成する。このようにして、後続のパターン化プロセスおよび電気めっきプロセス等において、比較的薄い基材を操作することができる。また、この製造方法により、奇数層または偶数層の基板を製造することが可能である。

(もっと読む)

導体構造要素及び導体構造要素を製造するための方法

硬質な支持体(12)を用意する工程と、前記硬質な支持体(12)上に銅の層(14)を電着によって形成する工程と、前記銅のコーティング(14)上に導電パターン構造(16)を適用し、次いでおそらくは部品を組み付ける工程と、前記支持体に少なくとも1つの電気絶縁層(24、28)を積層する工程と、前記硬質な支持体(12)を取り外す工程と、前記導電パターン構造(16、14、42)の露出が生じるように、前記硬質な支持体(12)の残りの銅のコーティング(14)を少なくとも部分的に除去する工程とを含む導体構造要素を製造するための方法。 (もっと読む)

多層配線基板及びその製造方法

【課題】銅箔の片側だけに配線層を積み上げて多層化するコアレス工法を用いても、反り量を抑制でき、作業性や歩留りのよい多層配線基板及びその製造方法を提供することを目的とする。

【解決手段】金属箔Aを回路加工して形成された第1層配線パターンと、この第1層配線パターン上に配置された絶縁樹脂層及びこの絶縁樹脂層上に配置された配線パターンを有する少なくとも1層の高層側の配線層と、を有する多層配線基板であって、前記高層側の配線パターンは、前記絶縁樹脂層上に金属箔とめっきにより形成された導体層を回路加工することにより形成され、前記第1層配線パターンより最も高層側の配線パターンの厚みが厚く、または前記第1層配線パターンより最も高層側の配線パターンの導体層残存率が大きく、または前記第1層配線パターン上の絶縁樹脂層より最も高層側の絶縁樹脂層の厚みが薄くなるように形成される多層配線基板及びその製造方法。

(もっと読む)

インダクタ内蔵部品

【課題】小型・薄型化が可能で、かつ十分なインダクタンスが得られるインダクタ素子を内蔵するインダクタ内蔵部品を提供する。

【解決手段】平面コイル層12(インダクタ素子)を内蔵したインダクタ内蔵部品10において、基板11上にn層(nは1以上の整数)の平面コイル層12を形成し、凹部14aを有する磁束漏洩防止金属キャップ14を、その凹部14aで基板11を収容するようにして装着する。磁束漏洩防止金属キャップ14は、鉄、コバルト、又はニッケルのような強磁性を示す金属材料からなり、平面コイル層12の上方から基板11の側面までを被覆する。これにより、平面コイル層12で発生した磁束の漏洩が防止され平面コイル層12のインダクタンスを高めることができる。

(もっと読む)

印刷回路基板およびその製造方法

【課題】基板内形成のための加熱制限があってもキャパシタ誘電体膜において高い比誘電率を得る。

【解決手段】基板内部の基板樹脂層3にキャパシタ10を埋め込んで形成する。その形成工程では、下部電極11を形成し、基板樹脂層3の耐熱温度以下、室温以上で結晶質金属酸化物を含むキャパシタ誘電体膜12を形成し、その上面で下部電極11と対向する上部電極13を形成する。

(もっと読む)

半導体パッケージとその製造方法

【課題】パッドと配線層との接続不良の発生防止と、製造過程における半導体パッケージの反りの発生防止と、最終的に形成される半導体パッケージの薄型化とを同時に達成することが可能な半導体パッケージとその製造方法を提供する。

【解決手段】この半導体パッケージの製造方法は、半導体チップが埋設された封止樹脂層を有する半導体パッケージの製造方法であって、支持基板2上に、パッド形成面4aを上向きにして半導体チップ4を配置する工程と、前記半導体チップ4が覆われるように、前記支持基板2上に封止樹脂層6を形成する工程と、前記半導体チップ4のパッド5の上面5aが表出するまで、前記封止樹脂層6の上部を研磨する工程と、を備える。

(もっと読む)

電子素子内蔵型印刷回路基板及びその製造方法

【課題】電子素子内蔵型印刷回路基板及びその製造方法を提供する。

【解決手段】本発明に係る印刷回路基板は、キャビティが形成された第1基板と、キャビティにフェースダウン方式で内蔵された第1電子素子と、第1電子素子の上側に積層され、キャビティにフェースアップ方式で内蔵された第2電子素子と、第1基板の上下面にそれぞれ積層された第2基板と、を含むことを特徴とする。

(もっと読む)

多層フレキシブル配線板

【課題】構成を簡素化でき、製造工程を簡略化できるとともに、耐屈曲性や耐屈折性に優れ、かつ薄型化が容易な多層フレキシブル配線板を提供すること。

【解決手段】本発明の多層フレキシブル配線板は、絶縁基板14と、絶縁基板14の両面に設けられた一対の導電層15、16と、一対の導電層15、16上にそれぞれ設けられた一対の絶縁層17、19と、一対の絶縁層17、19上にそれぞれ設けられ、めっき及び/又は導電ペーストにより、一対の導電層とカバーレイを介さずに電気的に接続された少なくとも1層の外層回路L3(18)、L4(20)と、を備えたことを特徴とする。

(もっと読む)

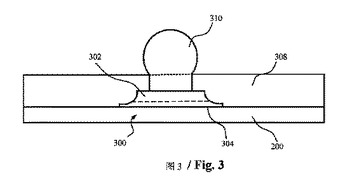

フレキシブル多層基板の金属層構造及びその製造方法

フレキシブル多層基板の金属層構造及びその製造方法を提供する。該金属層構造は、第1金属層(300)及び誘電層(308)を含み、該第1金属層(300)は本体(302)及び組み込みベース(304)から構成される。該本体(302)は、組み込みベースの上方に位置し、かつ組み込みベース(304)の底面積は本体(302)の底面積より大きい。誘電層(308)が第1金属層(300)の本体(302)及び組み込みベース(304)に被覆された後、第1金属層(300)の位置にビアホールを形成して、第1金属層(300)の本体(302)と誘電層(308)上の第2金属層(310)とが接合されるようにする。本体(302)及び組み込みベース(304)は一体成形され、かつ同時に形成することができる。該金属層構造をフレキシブル多層基板のパッド、又は金属回路として使用される場合、金属層と誘電層との間の分離現象を防止し、かつフレキシブル多層基板は高い信頼性を備える。  (もっと読む)

(もっと読む)

機能素子内蔵基板及びその製造方法、並びに電子機器

【課題】機能素子内蔵基板において、薄化と設計自由度を維持しつつ、放熱効果を十分に確保できる構造およびその製造方法を提供する。

【解決手段】絶縁層3と、該絶縁層に埋設される1以上の機能素子1を含む機能素子内蔵基板であって、該絶縁層3内部の該機能素子1の横方向周囲に配された放熱材5が該機能素子内蔵基板の側面部に露出するとともに、少なくとも一部がさらに基板面に直交する方向に亘って延在して形成されている(延在部40)ことを特徴とする機能素子内蔵基板。

(もっと読む)

多層プリント基板及びその製造方法

【課題】基板の製造時及び製造後に基板の撓みを防止し、支持体が基板の撓みを防止するとともにソルダレジスト層の機能を有するので、別途のPSR工程が不要になる。

【解決手段】本発明の製造方法は、両面または片面の銅張積層板に回路パターン(56)を形成し、その上部にビルドアップ層(57)を積層した後、ビルドアップ層(57)の上面にソルダレジスト層(58)を形成する。これにより、ビアホール(54)を持ち、一面に、回路パターン(56)を含む第1回路層が形成され、他面に、前記ビアホール(54)上に突出したソルダボール実装用接続パッドを含む第2回路層が形成された絶縁樹脂層(50)、前記第1回路層上に形成された多数の絶縁層及び多数の回路層を含むビルドアップ層(57)、及び前記ビルドアップ層(57)の最外層に形成されたソルダレジスト層(58)を含む。

(もっと読む)

多層プリント配線板の製造方法

【課題】絶縁層中にボイドが発生するのを防止することができると共に薄型化を図ることができる多層プリント配線板の製造方法を提供する。

【解決手段】多層プリント配線板の製造方法に関する。積層板の表面に形成された厚み105μm以上の導体パターン間の隙間に樹脂組成物を充填して前記導体パターンの表面と前記樹脂組成物の表面とを面一とし、次にこの面にプリプレグを介して金属箔を重ねた後、これを加熱加圧することによって積層成形する。

(もっと読む)

回路基板の製造方法

【課題】本発明は、小型化、軽量化、薄型化することが可能な回路基板を製造する方法を提供する。

【解決手段】本発明に係る回路基板の製造方法は、コア層10に、プリプレグシートからなるビルトアップ層20を積層して回路基板1を製造する方法である。未硬化状態のビルトアップ層20の一面に、配線パターン(第1配線パターン)21を形成し、配線パターン(第1配線パターン)21がコア層10側となるようにビルトアップ層20をコア層10に積層し、加熱しながら等方圧で加圧してコア層10にビルトアップ層20を圧着して配線パターン(第1配線パターン)21をビルトアップ層20に内蔵する。

(もっと読む)

プリプレグ、基板および半導体装置

【課題】本発明の目的は、薄膜化に対応することが可能であり、かつ回路パターンに応じて樹脂量を調整することが可能なプリプレグを提供することにある。また、本発明の目的は、上記プリプレグを有する基板および半導体装置を提供することにある。

【解決手段】本発明のプリプレグ10は、ガラス繊維で構成される繊維基材1と、繊維基材1の一方の面側に位置する第1樹脂層21と、繊維基材1の他方の面側に位置する第2樹脂層22とを有する。第1樹脂層21と第2樹脂層22とは組成が同一または異なる樹脂材料2で構成され、第1樹脂層21の厚さは、第2樹脂層22の厚さより厚く、プリプレグ10全体の厚さT0は40μm以下である。

(もっと読む)

多層プリント回路基板の製造方法

【課題】多層プリント基板の厚さを減少させるうえ、生産工程を短縮し、生産効率を増大させることが可能な多層プリント基板およびその製造方法の提供する。

【解決手段】多数の回路層および多数の絶縁層を含むビルドアップ層(108)、バンプがプリントされた前記ビルドアップ層(108)の一面の最外層回路層に形成される絶縁樹脂層(101)、および前記ビルドアップ層(108)の他面の最外層に形成される半田レジスト層(112)を含むことを特徴とし、一面にバンプがプリントされた絶縁樹脂層(101)の他面にビルドアップ層(108)、および半田レジスト層(112)を順次積層することにより製造される、多層プリント基板を提供する。

(もっと読む)

プリント回路基板及びそれの製造方法

【課題】プリント回路基板及びそれの製造方法が提供される。

【解決手段】本発明によるプリント回路基板は、第2層回路パターン及び第3層回路パターンが埋められた第1絶縁層と、前記第1絶縁層を間に置いて積層され、第1層回路パターンが形成された第2絶縁層及び第4層回路パターンが形成された第3絶縁層とを有する積層体と、前記回路パターンの電気的連結のための導電性ビアと、を含み、前記導電性ビアは、前記第1層回路パターンと前記第2層回路パターンを連結する第1導電性ビアと、前記第1層回路パターンと前記第3層回路パターンを連結する第2導電性ビアと、前記第2層回路パターンと前記第4層回路パターンを連結する第3導電性ビアと、前記第3層回路パターンと前記第4層回路パターンを連結する第4導電性ビアと、を含む。

(もっと読む)

61 - 80 / 335

[ Back to top ]