Fターム[5F004EA13]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | サイドウォール (408) | 側壁保護膜の形成 (258)

Fターム[5F004EA13]に分類される特許

21 - 40 / 258

プラズマ処理方法

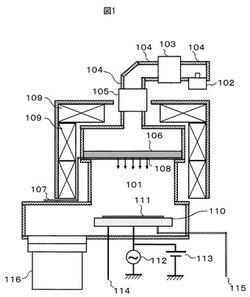

【課題】マイクロ波プラズマエッチングによるシリコン深溝トレンチの高速エッチングを実現することによる生産性の高いエッチング方法を提供する。

【解決手段】シリコン基板111やSOI(Silicon On Insulator)基板111に高アスペクト比(アスペクト比=トレンチ深さ/トレンチ幅)の深いシリコントレンチまたは穴を形成するプラズマエッチング方法において、マイクロ波によって生成されたプラズマを用い、プラズマを形成するマイクロ波は、高圧力、高マイクロ波出力においても安定したプラズマを形成するため、導波管104の一部にマイクロ波回転発生器105を設け、マイクロ波回転発生器105を通過したものであり、また、プラズマ形成に用いるガスとして少なくともフッ素を含むガスとO2の混合ガスを用い、かつ、試料台110に高周波電源112によりバイアス電圧を印加することにより深いシリコントレンチまたは穴を形成する。

(もっと読む)

シリコン基板のエッチング方法、及びシリコン基板のエッチング装置

【課題】シリコン基板に形成される凹部の加工精度を高めることのできるシリコン基板のエッチング方法及び該方法を用いるシリコン基板のエッチング装置を提供する。

【解決手段】シリコン基板に対してその厚さ方向に延びる凹部を形成する際に、シリコン基板を含む基板Sを収容する真空槽11内に六フッ化硫黄(SF6)ガスのプラズマを生成して、該シリコン基板の厚さ方向に延びる凹部を形成する。加えて、真空槽11内に三フッ化ホウ素(BF3)ガスのプラズマを生成して、上記凹部の内壁面にホウ素とシリコンとを含む保護膜を形成する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

レジストパターン形成方法およびそれを用いたパターン化基板の製造方法

【課題】レジストパターンの形成において、残膜をエッチングする工程後のレジストパターンの凸部の幅が、残膜をエッチングする工程前におけるレジストパターンの凸部の幅以上の所望の幅となることを可能とする。

【解決手段】凹凸パターンが転写されたレジスト膜2の残膜エッチング工程が、エッチングの際に堆積物4を生成する堆積性ガスを含有する第1のエッチングガスを用いて、レジストパターンにおける凸部の側壁に堆積物4が堆積しかつ残膜がエッチングされる条件でレジスト膜2をエッチングする第1のエッチング工程を含み、堆積物4を含めた上記凸部の幅が残膜エッチング工程前における上記凸部の幅以上の所望の幅となるように第1のエッチング工程以後の工程によってレジスト膜2をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

プラズマエッチング方法及び半導体装置の製造方法並びにコンピュータ記憶媒体

【課題】高アスペクト比のコンタクトホールを形成することができ、かつ、オーバーエッチング工程におけるミニマムバーの急激な減少を抑制することのできるプラズマエッチング方法及び半導体装置の製造方法並びにコンピュータ記憶媒体を提供する。

【解決手段】エッチストップ層上に形成された酸化シリコン膜にホールを形成するプラズマエッチング方法であって、酸化シリコン膜をエッチングするメインエッチング工程と、メインエッチング工程の後、エッチストップ層が少なくとも一部露出した状態で行うエッチング工程とを具備し、エッチストップ層が少なくとも一部露出した状態で行うエッチング工程は、処理ガスを、C4F6ガスとArガスとO2ガスとの混合ガスとした第1エッチング工程と、処理ガスを、C4F8ガスとArガスとO2ガスとの混合ガス、又は、C3F8ガスとArガスとO2ガスとの混合ガスとした第2エッチング工程とを交互に複数回繰り返して行う工程を含む。

(もっと読む)

プラズマ加工形状シミュレーション装置及びプログラム

【課題】ボッシュプロセスにより形成される加工形状を予測することができる、プラズマ加工形状シミュレーション装置及びプログラムを提供する。

【解決手段】加工処理対象物に関する条件、エッチングプロセスとデポジションプロセスとを一サイクルとした際のサイクル数を含むプロセスにおける条件及びシミュレーションに関する条件を設定する条件設定ステップ(STEP11)と、エッチングプロセスにおける条件に基づいたプラズマエッチングによる表面移動量を計算するエッチングプロセス表面移動量計算ステップ(STEP12)と、デポジションプロセスにおける条件に基づいたプラズマデポジションによる表面移動量を計算するデポジションプロセス表面移動量計算ステップ(STEP13)と、を備える。エッチングプロセス表面移動量計算ステップ(STEP12)とデポジションプロセス表面移動量計算ステップ(STEP13)とを条件設定ステップ(STEP11)にて設定されたサイクル数繰り返すことにより形成される形状を求める。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

半導体素子の製造方法

【課題】被処理基板のエッチングにおける面内均一性を向上させるとともに、丸みのある滑らかな底面を有する素子分離用トレンチを形成することができる半導体素子の製造方法を提供する。

【解決手段】シリコン基板51に素子分離用トレンチ59を形成するためのパターニングが施されたハードマスク57を形成する工程と、該ハードマスクをエッチング用マスクとして、希ガス、ハロゲンガス、および酸化性ガスを含むプロセスガスを供給し、所定の深さよりも浅い深さまでシリコン基板51をエッチングする第一工程と、該第一工程の後に、希ガス、ハロゲンガス、酸化性ガス、および堆積性ガスを含むプロセスガスを、シリコン基板51の中央領域および周縁領域にそれぞれ流量を制御して供給し、所定の深さD2までシリコン基板51をエッチングして素子分離用トレンチ59を形成する第二工程と、を備える製造方法とする。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】基板の温度が100℃以下の低温環境下において、基板上の被処理膜をエッチングする際のマスクを所定のパターンに適切に形成する。

【解決手段】ウェハWの被処理膜400上に反射防止膜401とレジストパターン402が形成される(図10(a))。レジストパターン402がトリミングされると共に、反射防止膜401がエッチングされる(図10(b))。ウェハWの温度を100℃以下に維持した状態でプラズマ処理を行い、レジストパターン402及び反射防止膜パターン403上に、100MPa以下の膜ストレスを有するシリコン窒化膜404が成膜される(図10(c))。シリコン窒化膜404がエッチングされ、レジストパターン402及び反射防止膜パターン403が除去されて、被処理膜400上にシリコン窒化膜パターン405が形成される(図10(d))。

(もっと読む)

マスク用材料、マスクの形成方法、パターン形成方法、及びエッチング保護膜

【課題】エッチング選択比の高いマスクを形成する技術を提供する。

【解決手段】エッチングによって被エッチング物をパターニングする際に用いるマスクを形成するためのマスク用材料であって、イソブチル基および/または環状炭化水素を有するシラン化合物からなることを特徴とするマスク用材料を提供する。また、エッチングによって被エッチング物をパターニングする際に用いるマスクの形成方法であって、パターン化されたホトレジスト上に上記マスク形成用材料を用いてALD法により共形膜を形成する工程、エッチバックして前記レジスト膜の側面にマスク形成用材料が残るように加工する工程、前記レジスト膜を除去する工程、とを有することを特徴とするマスクの形成方法を提供する。こうして形成したマスク形成用材料をマスクとしてエッチングすることで、被エッチング物に微細パターンを形成する

(もっと読む)

半導体発光素子の製造方法

【課題】 本発明は、半導体発光素子表面の微細構造体(輝度向上構造)の製造に好適に使用される単粒子膜エッチングマスクとその製造方法、該単粒子膜エッチングマスクを用いた微細構造体の製造方法および該製造方法で得られた微細構造体を光取り出し面に有する半導体発光素子に関する。

【解決手段】基板上に発光層を含む半導体多層膜を積層してなる半導体発光素子の製造方法において、下記式(1)で定義される粒子の配列のずれD(%)が10%以下である単粒子膜からなるエッチングマスクを前記半導体発光素子の光取り出し面上の少なくとも一部に形成し、ドライエッチングすることにより、前記光取り出し面上の少なくとも一部に微細構造体を形成する半導体発光素子の製造方法。

D(%)=|B−A|×100/A・・・(1)

(式(1)中、Aは前記粒子の平均粒径、Bは前記単粒子膜における前記粒子間の平均ピッチを示す。)

(もっと読む)

プラズマエッチング方法

【課題】レジストマスク、シリコンを含む膜及びシリコン層が上方側からこの順番で積層された基板に対して、レジストマスクのパターンを介してプラズマエッチング処理を行ってシリコン層に凹部を形成するにあたり、前記シリコンを含む膜のサイドエッチングの発生を抑えること。

【解決手段】窒化シリコン膜2をエッチングしてシリコン層1を露出させた後、塩素を含む処理ガスのプラズマ(イオン)を用いて当該シリコン層1を僅かにエッチングして、窒化シリコン膜2の側壁に塩素とシリコンとを含む付着物13を付着させる。この付着物13はシリコン層1よりもエッチングされにくい物質であり、更に塩素イオンは異方性エッチングを行うプラズマである。

(もっと読む)

基材の処理方法

【課題】本発明は、新規な優れた基材の処理方法を提供する。

【解決手段】本発明は、基材の処理方法であって、

(a)チャンバー中で、反応性のエッチングガスを用いるエッチングステップ、および先行するエッチングステップにより既にエッチングされた構造の部分の側壁上に保護ポリマーを堆積するための堆積ステップを含む周期的なプロセスを用いて、基材に概ね垂直な構造をエッチングすること、および

(b)基材の非存在下において、ステップ(a)における堆積ステップの実行によって物質が堆積したチャンバーを、洗浄することを含み、堆積に由来する物質の洗浄に続いて、チャンバーをO2と少なくともエッチャントガスの活性元素との混合物を含むプラズマに暴露することによって、エッチャントガス由来の物質を取り除いてチャンバーが洗浄されることを特徴とした、基材の処理方法である。

(もっと読む)

エッチングプロセスのための安定化したフォトレジスト構成

【課題】エッチレイヤに特徴を形成する方法を提供する。

【解決手段】第1のマスクが前記エッチレイヤ上に形成され、前記第1のマスクは、幅を有する複数のスペースを定義する。第1のマスクは横方向にエッチングされ、エッチングされた第1のマスクは、前記第1のマスクの前記スペースの前記幅より大きい幅を有する複数のスペースを定義する。前記エッチングされた第1のマスク上に側壁レイヤが形成され、前記側壁レイヤは、前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する複数のスペースを定義する。前記エッチレイヤ中に前記側壁レイヤを通して特徴がエッチングされ、前記特徴は前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する。前記マスク及び前記側壁レイヤは取り除かれる。

(もっと読む)

プラズマ処理方法及びプラズマ処理装置

【課題】エッチングステップとデポステップを交互に繰り返すプラズマ処理において、ステップ切換時のチャンバ内の圧力を安定させる。

【解決手段】基板21をエッチングするエッチングステップと、基板21に対して堆積により保護膜を形成するデポステップとを交互に繰り返してドライエッチングが行われるドライエッチング装置1は、基板21が収容されるチャンバ2、プラズマを発生させるためのアンテナ3と高周波電源部5A、ガス源7A,7Bから供給されるガスの流量調整部8A,8B、チャンバ2内の圧力を制御するための圧力制御バルブ12を備え、ドライエッチング開始後の2回目以降の前記エッチングステップと前記デポステップでは、それぞれ、予め定められた時間だけ圧力制御バルブ12の開度を直前のステップにおける開度で維持(開度制御モード)した後に、予め定められた圧力を維持するように前記バルブの開度を制御(圧力制御モード)する。

(もっと読む)

プラズマエッチング方法、及びプラズマエッチング装置

【課題】シリコン基板に挟まれた接着層をエッチングする際に、シリコン基板の積層方向へエッチングを進みやすくすることのできるプラズマエッチング方法、及びプラズマエッチング装置を提供する。

【解決手段】

接着層が、第1シリコン基板と第2シリコン基板とに挟まれた積層体30を真空槽11に搬入し、該積層体30に対し、第1シリコン基板と接着層とを貫通して積層体30の積層方向に延びる凹部を形成する。このとき、第1ガスのプラズマにより、上記積層方向に延びる凹部を第1シリコン基板の第1シリコン層に形成する工程と、第2ガスのプラズマにより、積層方向に延びる凹部を接着層に形成する第2エッチング工程とを実施する。加えて、第1シリコン層のエッチング工程と接着層のエッチング工程との間には、第1ガスと第2ガスとの混合ガスのプラズマにより、第1シリコン層と接着層との境界をエッチングする境界エッチング工程を実施する。

(もっと読む)

プラズマ処理方法

【課題】磁気中性線放電(NLD)プラズマエッチング装置のクリーニングの終点を制度良く検出することが可能なプラズマ処理方法を提供する。

【解決手段】磁気中性線放電(NLD)プラズマエッチング装置において、チャンバクリーニング処理の際に磁気コイルに流す電流値を、基板エッチング処理の際に前記磁気コイルに流す電流値よりも小さくすることにより、プラズマ中の分子種の時間変化をアンテナコイル電圧Vppの変化に反映させ易くして監視し、クリーニングの終点を検出する。

(もっと読む)

薄膜素子の作製方法及び半導体装置の作製方法

【課題】所定の層が水分などに一切曝されることない半導体装置の作製方法を提供することを課題とする。

【解決手段】第1の膜、第2の膜及び第3の膜をこの順に積層して形成し、第3の膜上にレジストマスクを形成し、レジストマスクを用いて第3の膜をエッチングすることでマスク層を形成し、レジストマスクを薬液により除去し、マスク層を用いて第2の膜と第1の膜をドライエッチングすることで、第2の層と第1の層を形成し、少なくとも第2の層と第1の層を覆って第4の膜を形成し、第4の膜をエッチバックすることで、少なくとも第1の層の側面のすべてを覆ってサイドウォール層を形成することで薄膜素子を作製する。

(もっと読む)

21 - 40 / 258

[ Back to top ]