Fターム[5F033HH12]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Cu (5,213) | Cu合金 (720)

Fターム[5F033HH12]に分類される特許

41 - 60 / 720

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

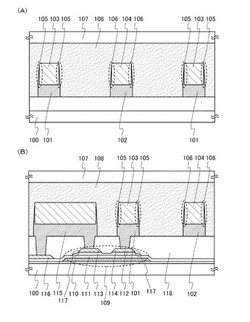

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な配線用膜を提供する。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層と、純CuまたはCu合金からなる層とを含む2層以上の積層構造を有することに要旨を有する配線用膜。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

インク受容層、インク受容層形成用塗布液、インク受容層の形成方法、及び導電パターンの形成方法

【課題】基板上に形成される、導電性と基板密着性が良好な導電パターンを形成することが可能なインク受容層の形成方法を提供する。

【解決手段】銅微粒子を含む導電性インクを塗布後に焼成により導電パターンを形成することが可能な、基板表面上に形成されるインク受容層で、該インク受容層が(i)非導電性無機粒子とバインダー樹脂からなる構造体でポリオールが5〜25質量%保持されたインク受容層(R1)、(ii)複数の貫通孔を有する多孔構造部を備えた非導電性無機材料構造体でポリオールが5〜80体積%保持されたインク受容層(R2)、又は(iii)複数の貫通孔を有する多孔構造部を備えた非導電性有機ポリマー構造体でポリオールが5〜80体積%保持されたインク受容層(R3)であり、前記ポリオールが分子内にヒドロキシル基を2個以上有していて常圧における沸点が100〜350℃である、インク受容層。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路装置用バリア材

【課題】従来のルテニウムバリア材と同様に優れた銅拡散の抑制効果を有し、供給性の点で問題がなく、比較的低コストの金属又はその金属を含む金属間化合物からなる新規な半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路用バリア材を提供する。

【解決する手段】バリア膜若しくはバリア膜とシード膜からなる複合膜の上に銅配線層を有する半導体集積回路装置の前記バリア膜を構成するバリア材として、単位結晶格子の最近接原子間距離(DM)がルテニウムの単位結晶格子の最近接原子間距離(DRu)に近い領域、具体的には、オングストローム(Å)単位で−0.200Å<(DM―DRu)<0.12Åの関係にあって、かつ融点若しくは変態点が650ケルビン(K)以上である金属又は金属間化合物を選択することを特徴とする。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

金属膜

【課題】配線金属膜の酸化を防止し、さらに、酸化防止を行うことで新たに発生した電解腐食も防止する。

【解決手段】基材としてのフィルム2上に、ITO膜3が形成され、その上に金属膜4が形成される。金属膜は、NiCu合金膜からなる第2保護膜41、Alよりも抵抗値が低く配線パターンとなる金属配線膜(Al−Nd合金)42、および、NiCu合金膜からなる第1保護膜43の順に積層されて構成される。

(もっと読む)

銅を主成分とする金属薄膜のエッチング液組成物

【課題】

本発明の課題は、銅および銅合金薄膜を含む金属積層膜パターンを精度良くエッチング加工し、優れたパターン形状を形成し、かつ実用性に優れた安定で液寿命の長いエッチング液組成物、およびかかるエッチング液組成物を用いたエッチング方法を提供することにある。

【解決手段】

本発明は、銅からなる層と、銅を含む銅合金からなる層とを有する金属積層膜を、特定の組成を有する、りん酸、硝酸、酢酸および水を配合してなるエッチング液組成物を用いてエッチングするエッチング方法、およびそのエッチング液組成物に関する。

(もっと読む)

半導体用銅合金配線及びスパッタリングターゲット並びに半導体用銅合金配線の形成方法

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜5wt%を含有し、Sb,Zr,Ti,Cr,Ag,Au,Cd,In,Asから選択した1又は2以上の元素の総量が10wtppm以下、残部Cuである自己拡散抑制機能を備えた半導体用銅合金配線。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

シリコン配線基板およびその製造方法

【課題】金属配線層間の絶縁を良好に維持することが可能で、シリコン基体上の絶縁層と金属配線層との密着性を向上したシリコン配線基板を提供する。

【解決方法】シリコン基体上に形成された二酸化ケイ素を主成分とする絶縁層と、前記絶縁層上に形成され、絶縁層のSiと酸素を介してシロキサン結合されたシラノール基もしくはアルコキシシラン基を有する有機単分子皮膜と、前記有機単分子皮膜に担持された触媒金属と、前記有機単分子皮膜に前記触媒金属を介して形成されたシード層と、前記シード層上に形成された金属からなる配線層とを具備したことを特徴とするシリコン配線基板。

(もっと読む)

41 - 60 / 720

[ Back to top ]