Fターム[5F033JJ33]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 窒化物 (3,695) | TiN (1,991)

Fターム[5F033JJ33]に分類される特許

101 - 120 / 1,991

電気光学装置の製造方法

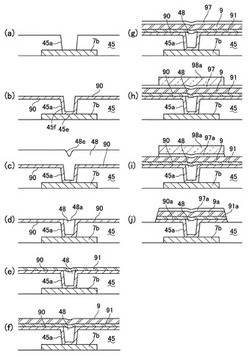

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板貫通電極の周囲に形成される絶縁分離部において、埋め込まれる絶縁膜が接合面を有していると、基板裏面の研削後の絶縁分離部は、接合面が基板主面から基板裏面に達することで、機械的強度が低下しやすく、貫通電極に応力を印加した場合に絶縁分離部の内側領域が孤立しやすい。

【解決手段】絶縁分離部5に埋め込まれる絶縁膜を第1の絶縁膜3と第2の絶縁膜4の少なくとも2段の積層構造とすることで、第1の絶縁膜3の接合面3Sと第2の絶縁膜4の接合面4Sとが第2の絶縁膜4の底面の接合面のない領域で分断され、機械的強度が増加し、絶縁分離部の内側領域の孤立を阻止することができる。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

101 - 120 / 1,991

[ Back to top ]