Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

21 - 40 / 405

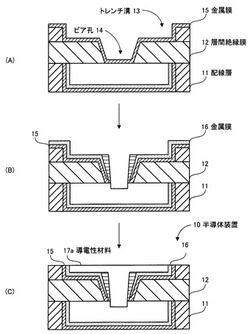

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

材料を付着させる方法

【課題】改良された付着プロセスを提供すること。

【解決手段】ビームを使用して、自発的反応の開始をサポートする条件を提供するように準備された表面の領域における前駆体ガスの自発的付着によって、材料を、所望のパターンに付着させる。いったん反応が開始されると、ビームが存在しなくなっても、反応が開始された表面の領域において反応は継続する。

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

半導体装置の製造方法

【課題】レーザー光の照射による滓の発生を抑えるようにするとともに、分断後の低誘電率膜にダメージを与えないようにする。

【解決手段】半導体ウエハ61の一方の面61aの上に形成された低誘電率膜21をドライエッチングすることにより低誘電率膜21に溝21aを形成し、低誘電率膜21の上に封止層41を形成するとともに、低誘電率膜21の溝21a内に封止層41の一部を埋め込み、半導体ウエハ61及び封止層41を低誘電率膜21の溝21aに沿って分割する。

(もっと読む)

半導体装置、および半導体装置の検査方法

【課題】高抵抗回路の面積の狭小化を図り、集積率の高い半導体装置への高抵抗回路の形成を容易とする。

【解決手段】配線層2に形成された下層配線20および下層配線22と、配線層2上に形成された層間絶縁膜12と、層間絶縁膜12に形成され、下層配線20と接続するビア30と、層間絶縁膜12に形成され、下層配線22と接続するビア32と、層間絶縁膜12上に形成され、ビア30とビア32とを接続する上層配線24と、を備え、ビア30およびビア32の抵抗値は、上層配線24の抵抗値よりも大きい。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いる配線形成方法で、特に最上層の配線を含む上層配線を形成する場合、接続孔の周囲に生ずるクラウンフェンスを容易に除去して信頼性の高い半導体装置を提供する。

【解決手段】 接続孔19a、19b上に形成された開口を有するマスク層21をマスクとして、第3絶縁膜17および第3絶縁膜17より密度の小さい、あるいは比誘電率が小さい第2絶縁膜16をエッチングして配線溝22を形成すると、接続孔19bに埋め込まれた有機性材料20の突出部と同時に、第2絶縁膜16の構成材料を主成分とするクラウンフェンス23が生ずる。これに対しマスク層21の除去工程を兼ねるなどの処理において、少なくとも配線溝22の内部にプラズマ処理を施した後、第2絶縁膜16を溶解可能な処理液で処理し上記のプラズマ処理で変質したクラウンフェンス25を選択的に除去する。

(もっと読む)

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

21 - 40 / 405

[ Back to top ]