Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

81 - 100 / 405

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

貫通電極の形成方法、及び半導体基板

【課題】高温雰囲気を維持した状態で溶融金属をハンドリングする必要をなくして工程及び装置を簡略化することができ、また導電ペーストを用いる場合と比較して高密度に金属を貫通孔内に充填することができる貫通電極の形成方法を提供する。

【解決手段】Si基板10の表面に開口を有する第1の非貫通孔21と、第1の非貫通孔21の底部に第1の非貫通孔21よりも小さな開口を有する第2の非貫通孔22とを形成し、第1の非貫通孔21の底部に固体金属50を載置する。Si基板10を減圧雰囲気下に置き、固体金属50の軟化点近傍まで加熱する。加熱状態を維持して減圧雰囲気から加圧雰囲気に移行し、軟化或いは溶融した金属50を第2の非貫通孔22に充填する。

(もっと読む)

ドライエッチング方法及び金属薄膜のパターニング方法

【課題】難エッチング材料を不活性ガスによりエッチングする際に残渣なく加工する方法を提供する。

【解決手段】難エッチング性の金属薄膜2上に、断面形状がハンマーヘッド型となるようにレジスト4を形成した後に前記金属薄膜をドライエッチングし、その後前記レジストを除去する。前記ハンマーヘッド型の断面形状を有するレジストパターンは、現像液に対する溶解速度が異なる2種類のレジストを積層塗布して露光・現像することによって得る。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、固体撮像装置の駆動方法、及び電子機器

【課題】固体撮像装置が形成されるチップ面積の縮小化が図られ、チップ単体のコストの低減が図られた固体撮像装置を提供する。また、その固体撮像装置を用いることにより、小型化が図られた電子機器を提供する。

【解決手段】本発明の固体撮像装置は、光電変換部PDが形成された第1の基板80と、電荷蓄積容量部61及び複数のMOSトランジスタが形成された第2の基板81が張り合わされた構成とされている。また、第1の基板80と、第2の基板81にはそれぞれ接続電極(26,27,56,57)が形成されており、第1の基板80と第2の基板81は、接続電極により電気的に接続されている。これにより、グローバルシャッタ機能を有する固体撮像装置をより小さい面積に形成することが可能となる。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】一般的なウエハ・レベル・パッケージ・プロセスでは、メッキ・プロセス中におけるスクライブ領域のアルミニウム系パッド電極の腐食を防止するために、製品領域における有機系保護膜と同層のパッド保護用樹脂膜でパッド電極をカバーしている。しかし、これでは再配線形成後にスクライブ領域のパッド電極に対するプローブ検査が実行できない。

【解決手段】本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置の製造方法において、チップ領域およびスクライブ領域の有機系保護膜を相互に連結した一体の膜パターンとし、ペレタイズ工程においては、スクライブ領域中央部の有機系保護膜を含む表層部分を先ず、レーザ・グルービングで除去することで幅広の溝を形成し、その後、この溝内の中央部をダイシング処理することで、ここのチップ領域に分離するものである。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ビアホールの微細化及び高アスペクト比化が進むと、銅からなるシード層でビアホールの内面を連続的に覆うことが困難になる。

【解決手段】 半導体基板(10)の上に絶縁膜(20)が形成されている。絶縁膜に凹部(21)が形成されている。凹部の内面を第1の導電膜(22)が覆う。島状組織(25)が、第1の導電膜の表面に離散的に分布する。島状組織は、銅に対して、第1の導電膜の濡れ性よりも高い濡れ性を有する。凹部が、銅または銅合金からなる導電部材(31)で充填されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において歩留まりを向上させること。

【解決手段】シリコン基板30の上方に金属からなる第1の配線66を形成する工程と、第1の配線66の上に層間絶縁膜69を形成する工程と、第1の配線66の表面が露出する開口69aを層間絶縁膜69に形成する工程と、開口69aの内面及び層間絶縁膜69の表面に、上記金属の拡散を抑制するバリアメタル膜72を形成する工程と、バリアメタル膜72上に第1の導電膜73を形成する工程と、第1の導電膜73の表面を化学機械研磨法により研磨し、バリアメタル膜72の表面を露出させる工程と、開口69aの内の第1の導電膜73上及びバリアメタル膜72上に、第2の導電膜80を形成する工程と、第2の導電膜80を、開口69aよりも拡大した領域に残して選択的に除去し、第2の配線80aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置、半導体装置の製造方法、貫通電極、貫通電極の製造方法、発振器、及び電子機器

【課題】貫通電極と半導体基板との間でリーク電流が発生することを抑制することができる半導体装置、半導体装置の製造方法、貫通電極、貫通電極の製造方法、発振器、及び電子機器を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の第一の面に形成された第一の導電膜と、第一の面に略平行な第二の面に形成された第二の導電膜と、半導体基板に形成された貫通孔に配設されており、当該貫通孔に倣う形状を有し、第一の導電膜と第二の導電膜とに接続された貫通電極と、を有し、貫通孔は、第一の面及び第二の面に略垂直な側壁部と、側壁部と第一の面又は第二の面とを接続するそれぞれ1以上の接続壁とを備える。

(もっと読む)

半導体装置の製造方法

【課題】工程数の増加を抑えながら、ビア間の耐圧の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】配線2上に低誘電率膜5及び6を形成した後、低誘電率膜5及び6上にハードマスク7、8及び9を形成する。ハードマスク7〜9上にレジストマスクを形成する。レジストマスクを用いて低誘電率膜5及び6にビアホール11を形成する。レジストマスクをアッシングする。このとき、レジストマスクから生じる飛散物をビアホール11の少なくとも側面に付着させて保護膜12を形成する。その後、ビアホール11を配線2まで到達させ、ビアホール11内に導電材を埋め込む。

(もっと読む)

半導体装置、およびその作製方法

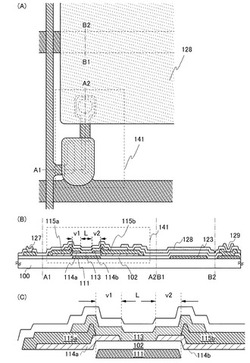

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】はんだ直接付けとワイヤボンディングとを両立できるアルミ電極を半導体チップ上に具備した半導体装置を提供する。

【解決手段】半導体チップ1に設けられたAl電極4上に生成したAl酸化皮膜5の適当な箇所に、該皮膜5を貫通してAl電極4まで届く微小金属11を形成させており、酸化物貫通微少金属を具備した一種類のAl電極をはんだ直接付け及びワイヤボンディング両用とすることが出来る。

(もっと読む)

半導体装置およびそれを用いた電子機器ならびに半導体装置の製造方法

【課題】本発明は、半導体基板の凹部内に形成される構成要素を有する半導体装置において歩留の低下およびデバイスの信頼性の低下を防止することが可能な半導体装置およびそれを用いた電子機器ならびに半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明の半導体装置は、絶縁膜8および貫通電極6が形成される貫通孔7が形成された半導体基板1を備え、半導体基板1の貫通孔7は、深さ方向に徐々に開口径が小さくなる形状を有し、貫通孔7の内壁には、貫通孔7の開口端よりも開口径が小さい段が形成されている。

(もっと読む)

ヒューズ式スルー・シリコン・ビアを有する3Dチップ・スタック

【課題】シリコン・チップ中のプログラム可能ヒューズ式スルーシリコン・ビア(TSV)を、同一のチップ中の非プログラム型TSVと併せ提供する。

【解決手段】該プログラム可能ヒューズ式TSVには、該TSV構造内に、チップ表面コンタクト・パッドに隣接するTSVの導電路の断面を限定する側壁スペーサを有する部域を用いることができる。プログラミング回路による十分な電流の印加により、金属のエレクトロマイグレーションが生じ、コンタクト・パッド中にボイド、しかしてオープン回路、が生成される。プログラミングは、多階層チップ・スタック中の2つの隣接するチップ上の相補的回路によって実行することができる。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置に形成される配線表面の酸化物部を選択的に除去する。

【解決手段】ダマシン配線構造を有する半導体装置を製造するに際し、配線表面を、Xeのプラズマで逆スパッタリングする。本発明によれば、Xeのプラズマガスで逆スパッタリングすることにより、配線表面の酸化物部等を選択的に効率よく除去でき、ダマシン配線構造において、上下配線間のコンタクト抵抗の増大を回避できる。また、配線の上に形成されたCFなどの絶縁膜へのダメージを抑制でき、絶縁膜の誘電率変動も抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

81 - 100 / 405

[ Back to top ]