Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

101 - 120 / 405

半導体装置及びその製造方法

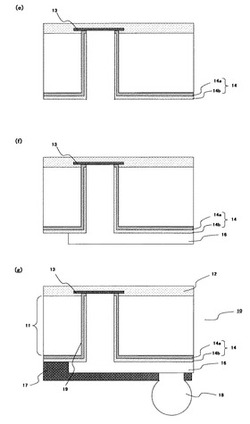

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

フォトセンサ及び表示装置

【課題】マトリクス状に配置した光電変換素子が捉える光の強度分布を、再現よく電気信号に変換して取り出せる大型のエリアセンサおよび、エリアセンサを搭載した書き込み速度が速く、表示ムラが少ない表示装置を提供する。

【解決手段】インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタは、大面積基板にマトリクス状に配置することが容易であり、また特性にバラツキが少ない。インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタで構成した特性にバラツキが少ない増幅回路と表示素子の駆動回路を用いて、マトリクス状に配置したフォトダイオードが捉える光の強度分布を再現よく電気信号に変換して取り出し、マトリクス状に配置した表示素子をムラなく駆動する。

(もっと読む)

配線構造体の製造方法及び配線構造体

【課題】 横方向(基板表面に平行な方向)にカーボンナノチューブを成長させるためには、側壁に平坦かつ微小な表面を持つ触媒膜を形成する必要がある。ところが、このような触媒膜を形成することは困難である。

【解決手段】 基板表面の相互に離隔した2つの縦配線領域に、第1の厚さの縦配線用触媒膜を形成し、1つの縦配線領域から他の縦配線領域まで連続する横配線領域に、第1の厚さよりも厚い第2の厚さの横配線用触媒膜を形成する。縦配線用触媒膜及び横配線用触媒膜の上に、カーボンを含む構造体を気相成長させる。気相成長の初期段階には、縦配線用触媒膜及び横配線用触媒膜の上にグラファイトが形成され、その後、縦配線領域の前記グラファイトと基板との間にカーボンナノチューブが成長し、横配線領域の前記グラファイトが、縦配線領域に成長したカーボンナノチューブによって中空に支持されるように第1の厚さ及び第2の厚さが設定されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐ。

【解決手段】半導体装置100は、基板(不図示)上に形成され、太幅配線溝106が表面に形成された層間絶縁膜104と、層間絶縁膜104の太幅配線溝106を埋め込んで形成され、バリアメタル膜110および銅膜116により構成された太幅配線120とを含む。太幅配線溝106の底面には、角部に選択的に凹凸114が形成され、凹凸114上にバリアメタル膜110が形成されている。

(もっと読む)

薄膜トランジスタ、表示装置、およびそれらの作製方法

【課題】薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及びその作製方法を提供する。また、画質を向上させることが可能な表示装置及びその作製方法を提供する。

【解決手段】また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トランジスタである。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

貫通電極配線の製造方法

【課題】複雑な工程を用いることなく、コストの増加や破損の発生などを抑制した状態で、より均一な深さの孔部を形成することで貫通電極配線が形成できるようにする。

【解決手段】酸化シリコン層104をマスクとしたRIEにより、シリコン基板101を選択的にエッチングすることで、シリコン基板101の一方の面(埋め込み酸化層102との界面)に到達する貫通孔106を形成する。貫通孔106の形成のためのエッチング処理(REI)においては、シリコン基板101の深さ方向に、シリコン基板101と埋め込み酸化層102との界面までしかエッチングが進行しない。この結果、シリコン基板101の板厚が均一であれば、貫通孔106の深さも均一に形成されるようになる。

(もっと読む)

半導体装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜として低誘電率膜を用いて配線溝を形成する際のダメージ層の形成による配線間容量の増加を抑制する。

【解決手段】低誘電率膜114の側壁に形成されたダメージ層130を除去する工程(図3(a)、3(b))と、化学気相成長法により第2の保護絶縁膜134を形成し、第1の保護絶縁膜116および低誘電率膜114の側壁を第2の保護絶縁膜134で覆って第2の凹部136cを形成する工程(図3(c))と、配線溝136dが低誘電率膜114の表面に選択的に第2の保護絶縁膜134が形成された側壁を有するように、第2の保護絶縁膜134をエッチバックして成形する工程(図3(d))とにより配線溝136dを形成する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

ビア配線を作るための方法

この発明は、電子デバイス用の基板(3)の下側(5)から基板(3)を少なくとも部分的に通って基板(3)の上側(4)に向かうビアホール(9)またはビア(7)を形成する方法を提供する。この方法は、ビアホール(9)の第1の縦方向部分(11)をエッチングするステップと、ビアホール(9)の第2の縦方向部分(12)をエッチングするステップとを含み、それにより、第1の縦方向部分(11)および第2の縦方向部分(12)はビアホール(9)を実質的に形成し、ビアホール(9)に狭窄部(23)が形成される。狭窄部(23)はビアホール(9)の開口部(24)を規定し、この方法は、狭窄部(23)がエッチングマスクとして機能している状態でエッチングすることによってビアホール(9)を開けるステップをさらに含む。ビアは、ビアホールを導電性材料で少なくとも部分的に充填することによって形成される。ビアを含む電気デバイス用の基板も提供される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法による配線パターン形成の際、低誘電率膜を層間絶縁膜に使った場合においてもビアホールや配線溝の側壁面における損傷や変形の発生を抑制し、同時に、下側配線パターンと上側配線パターンとのコンタクト抵抗を低減する半導体装置の提供。

【解決手段】活性素子を有する基板と、前記基板上において前記活性素子を覆う第1の層間絶縁膜と、前記第1の層間絶縁膜中に埋設された第1の配線層43Cuと、前記第1の層間絶縁膜上に形成された第2の層間絶縁膜52と、前記第2の層間絶縁膜中に埋設された第2の配線層と、を備え、前記第2の配線層は配線パターンと、前記配線パターンから延在し前記第1の配線層を構成する導体パターンの表面と直接に接触するビアプラグ50Vとを有し、前記配線パターンの底面および側壁面、および前記ビアプラグの側壁面は拡散バリア膜49A,49Bにより覆われることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンとキャップ層との界面を伝うCuの拡散を抑制し、同時にCu配線パターンの抵抗の増大を抑制するCuダマシン配線の製造法を提供する。

【解決手段】基板41上に側壁面と底面とにより画成された凹部を有する絶縁膜45を形成する。側壁面のうち、上端部を含む上側の第1の部分Dを覆い、凹部の底面と下側の第2の部分においては前記絶縁膜が露出するように覆う、金属膜47を形成する。凹部の側壁面と底面とを連続的に覆う導電性拡散障壁膜48を形成する。銅を充填し銅配線パターン49A、49B、49Cとする。絶縁膜上と銅配線パターンの表面を覆う絶縁性拡散障壁膜49を形成する。熱処理により、銅配線パターンと絶縁性拡散障壁膜との界面に、金属元素の濃集領域49Dを形成する。金属元素の濃集領域では、金属膜を構成する金属元素の濃度が、銅配線パターン中よりも高い。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させる。

【解決手段】第1の半導体チップ100と第2の半導体チップ200とが貼り合わされている。第1の半導体チップ100の表面部に電極パッド104が形成されている。第2の半導体チップ200中に貫通ビア114が形成されている。電極パッド104には掘り込み部111が形成されており、当該掘り込み部111内に貫通ビア114の底部が埋め込まれている。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

101 - 120 / 405

[ Back to top ]