Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

41 - 60 / 405

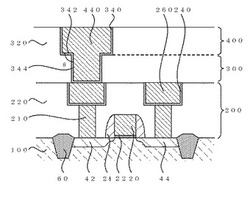

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイシング等で半導体装置を個片化する際に加工のダメージ又は膜の残留応力などに起因して発生する、基板上の膜の剥離を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置101,102の周辺すなわち個片化のための加工ラインの近傍の基板1上に溝6を形成する。その溝の内部では基板上に成膜される薄膜が少なくとも1部で不連続となることにより、万一、半導体装置の端部から膜剥がれが発生したとしても、この溝部でその進行を阻止する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグを、配線のバリア層に安定して接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、バリア層を介して配線に接続されたコンタクトプラグ、第1及び第2の絶縁膜を有する。第1の絶縁膜は、配線及びバリア層の側面を覆い少なくともバリア層よりも上方で配線が延在する方向と直交する方向の幅が狭まる傾斜面を有し、バリア層の上面の一部を露出すると共に配線及びバリア層の側面を露出させないように形成された開口部を備える。第2の絶縁膜は、開口部の内側を除き第1の絶縁膜上に形成され、かつ開口部を備える。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】外力を受けても変形あるいは破壊しにくい半導体装置の構造及びその製造方法を提供する。

【解決手段】半導体基板1表面に第1の掘り込み部を形成する。複数の配線電極3は第1の掘り込み部に埋め込まれた埋め込み部と半導体基板1上に露出する露出部とからなる。複数の配線電極のうち所定の配線電極3間にエアーブリッジ電極6が設けられている。配線電極3とエアーブリッジ電極6との接続は、配線電極3の露出部に第2の掘り込み部を形成し、エアーブリッジ電極6の脚部の接続部を第2の掘り込み部に埋め込むことによって行う。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】バリアメタルのステップカバレッジを向上させるボーダレスコンタクト構造を有する半導体装置を提供する。

【解決手段】低抵抗金属層と高融点金属元素を含む第1のバリアメタル膜を順次積層した構造の配線パタ―ン42Aと、配線パタ―ンを覆う層間絶縁膜43と、層間絶縁膜中に形成され、配線パタ―ンの上面の一部と側壁面の一部を露出し、さらに配線パタ―ンに、露出上面および露出側壁面を連結して形成された斜面をも露出斜面42dとして露出するビアホール43Aと、ビアホールの側壁面、露出上面および露出側壁面、さらに前記露出斜面に形成された、少なくとも低抵抗金属層の構成元素および高融点金属元素を含む導電性側壁膜43bと、導電性側壁膜を覆い、高融点金属元素を含む第2のバリアメタル膜と、前記第2のバリアメタル膜を介して充填し、前記第2のバリアメタル膜に接する導電性プラグと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

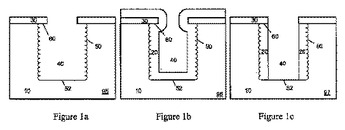

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

配線基板及び配線基板の製造方法

【課題】 貫通電極と配線層との間における電気抵抗の増加を抑制できる配線基板及び半導体装置を提供する。

【解決手段】 半導体基板と、半導体基板の少なくとも上面に形成され、導体層及び第1絶縁層を有する配線層と、半導体基板及び配線層の第1絶縁層を貫通する貫通電極と、半導体基板と貫通電極との間に形成された第2絶縁層と、を備える配線基板であって、貫通電極は、配線層の第1絶縁層を貫通する第1導電部と、半導体基板を貫通し、第1導電部と電気的に接続し、第1導電部の断面積よりも大きい断面積を有し、且つ導体層と電気的に接続する段差面を含む第2導電部と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体素子の製造方法

【課題】 デュアルダマシンプロセスを同一チャンバ内で行っても、再現性よくビアホールを貫通させる技術が望まれる。

【解決手段】 層間絶縁膜上の第1のマスク膜及び層間絶縁膜に、層間絶縁膜の厚さ方向の途中まで達するビアホールを形成する。第1のマスク膜の上に、下層レジスト膜を形成し、その上に、配線溝に対応する開口を有する第2のマスク膜を形成する。チャンバ内において、O2とCOとのプラズマを用い、下層レジスト膜をエッチングするとともに、ビアホール内の一部には、下層レジスト膜を残す。下層レジスト膜の開口の平面形状が転写された開口を、第1のマスク膜に形成するとともに、下層レジスト膜を除去し、ビアホールをさらに掘り下げて、下層配線を露出させる。層間絶縁膜を厚さ方向の途中までエッチングして配線溝を形成する。配線溝及び前記ビアホール内を、導電部材で埋め込む。

(もっと読む)

41 - 60 / 405

[ Back to top ]