Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

141 - 160 / 405

導電部材の形成方法、電子デバイスの製造方法、および、電子デバイス

【課題】基板に与える損傷を抑制できる導電部材の形成方法を提供する。アンダーカットの発生を抑制できる導電部材の形成方法を提供する。

【解決手段】基板を準備する段階と、基板の少なくとも一部を覆うリフトオフ層を形成する段階と、リフトオフ層に、基板の表面の一部を露出させる第1開口部を形成する段階と、リフトオフ層と第1開口部に露出した基板の表面とを覆うシード層を形成する段階と、シード層の表面に、レジスト層を形成する段階と、レジスト層に、少なくとも一部が第1開口部と重なり、かつ、シード層の一部を露出させる第2開口部を形成する段階と、第2開口部の内部に、導電部材を形成する段階と、レジスト層の少なくとも一部を除去する段階と、リフトオフ層をリフトオフ法により除去して、レジスト層とリフトオフ層との間のシード層を除去する段階とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、マスクを追加することなく、周辺ロジック部で形成されるクラッド配線構造の配線を1層に抑えた半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明の1つの実施形態は、(a)クラッド配線構造を採用する第1配線が形成された層上の磁気メモリ部に磁気トンネル接合構造MTJを形成する工程と、(b)磁気メモリ部及び周辺ロジック部上に層間絶縁膜6を堆積し、磁気トンネル接合構造MTJ上の層間絶縁膜6にクラッド配線構造を採用する第2配線を形成する工程と、(c)第2配線の一部を選択的にエッチングすることで第2配線にリセス部42を形成する工程と、(d)リセス部42を利用してセルフアラインにて第2配線の上部にクラッド部41を形成する工程と、(e)クラッド部41を形成後に周辺ロジック部のロジック配線を形成する工程とを備える半導体装置を製造する方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗およびビア抵抗のばらつきを配線層全体として抑制できる半導体装置およびその製造方法を提供する。

【解決手段】ビア深さBDEの深い第1のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗は、ビア深さBDEの浅い第2のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗よりも小さくなっている。

(もっと読む)

銅相互接続配線、ならびにそれを構成するための方法および機器

【課題】ガスクラスターイオンビーム処理プロセスの適用により、集積回路の相互接続構造に使用される、銅の相互接続配線層の表面上で、層をキャップ化する、改良された集積相互接続、集積回路の構造を形成する方法ならびに機器である。

【解決手段】

銅の拡散が抑制され、電気泳動寿命が向上し、選択金属キャップ化技術の使用、およびそれに付随した問題が解消される。銅のキャップ化処理、清浄化処理、エッチング処理、および膜形成処理用の、ガスクラスターイオンビーム処理モジュールを含む、各種クラスターツール構成について示した。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細コンタクト孔の形状寸法を安定させつつ、コンタクト抵抗ばらつきを低減することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11上にニッケルを含む金属シリサイド層12を形成し、その最表面12aを窒化した半導体装置を構成する。この構造によれば、金属シリサイド層最表面12aの窒化により、金属シリサイド層12中に存在するシリコンのダングリングボンドと窒素が結合するため、金属シリサイド層12中への酸素の拡散を抑制することができる。したがって、金属シリサイド層12の酸化による電気的絶縁を低減できるため、コンタクト抵抗を安定化することができる。

(もっと読む)

半導体デバイス内でのビアパターニングにおける金属キャップ層の侵食を低減する方法

【解決手段】

半導体デバイスの高性能な金属化システムにおいてビア開口をパターニングする間、開口(221A)が導電性キャップ層(213)を通って延び、適切なイオン衝撃が確立されて下層の金属領域(212)の材質が導電性キャップ層(213)の露出した側壁部分へ再分配され、それにより保護材質(212P)が確立される。その結果、後続のウエット化学的エッチング処理(215)において、導電性キャップ層(213)の過度な材質除去の可能性を大幅に低減することができる。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

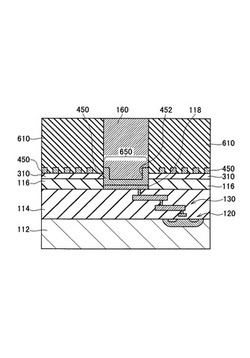

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】一般に電流量確保のため、ショットキー接合領域上に多数のコンタクト電極をマトリクス上に密集配置することが行われ、コンタクトホールの底のシリサイド層の表面をスパッタ・エッチング処理することが広く行われているが、このようにショットキー接合領域上に電極を配置した構造では、このスパッタ・エッチング量の変化により、ショットキー・バリア・ダイオードの逆方向リーク電流が変動する問題を解決するため、特性ばらつきの少ないショットキー・バリア・ダイオード(SBD)の半導体集積回路装置への組み込み技術を提供する。

【解決手段】周辺の素子分離領域に接したガードリング9上に、コンタクト電極11を配置したショットキー・バリア・ダイオードを有する半導体集積回路装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体基板のストリートに合金層を形成すること無く、しかもバリア層の横方向エッチングであるサイドエッチング量が少ない半導体装置および半導体装置の製造方法を提供する。

【解決手段】 半導体装置の入出力端子となる電極パッド2と、電極パッド2上に順次設けるバリア層および共通電極層6と、この共通電極層6上に設ける突起電極11を有する半導体装置において、バリア層は、2層からなるとともに、突起電極11材料または共通電極層6材料と電極パッド2材料とが相互に拡散することを抑制する材料からなり、共通電極層6側の第2のバリア層5は、電極パッド2側の第1のバリア層4より膜厚が薄い半導体装置およびその製造方法により、第2のバリア層5のサイドエッチング量を少なくすることが可能となり、さらに半導体基板のストリートに合金層が形成されることはない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 耐湿(耐水分、耐水素)性の優れた強誘電体膜を有するキャパシタのパッド構造を備え、パッドに傷が生じても、水素、水分に対する耐性を回復することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板の上方に電極間に挟まれた強誘電体膜を備えたキャパシタを形成する工程と、半導体基板の上方にキャパシタの電極と電気的に接続されるパッド電極を形成する工程と、半導体基板の上方にパッド電極を保護する保護膜を形成する工程と、保護膜にパッド電極の少なくとも一部が露出する開口部を形成する工程と、パッド電極の表面に測定端子を当てる工程と、測定端子を当てたパッド電極の表面をエッチングする工程と、保護膜とパッド電極の開口部を覆う水素吸蔵膜を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

配線用セルフアライン(自己整合)バリア層

集積回路中の銅線を完全に取り囲んでいるケイ酸マンガン層及び窒化ケイ素マンガン層を組み込んだ集積回路用の配線構造、及びその製造方法を提供する。ケイ酸マンガンは、銅が配線から拡散しないためのバリアを形成し、それにより、絶縁体が磁気尚早に損しないよう保護し、トランジスタが銅により劣化しないように保護する。また、ケイ酸マンガン及び窒化ケイ素マンガンは、銅と絶縁体の間の強い接着を促進し、これゆえに製造及び使用の間のデバイスの機械的な完全性が保持される。また、銅−ケイ酸マンガン界面及び窒化ケイ素マンガン界面における強い接着は、デバイスの使用の間の銅のエレクトロマイグレーションによる損傷から保護する。また、マンガン含有シースは、銅がその周囲の酸素又は水により腐食しないよう保護する。 (もっと読む)

半導体基板の電解めっき方法および電解めっき装置

【課題】貫通孔を有するシリコンウエハの貫通孔にオーバーハング形状や内部ボイドがなくめっきを充填する方法を提供すること。

【解決手段】シリコンウエハ内の貫通孔開口部と同位置に開口部を有するプレートを一定の距離をおいてシリコンウエハの貫通孔開口部にプレート開口部を合わせて、めっき電極側に向けて配置してめっきを行う。プレート開口径は貫通孔開口径より少し小さくする。プレート開口径と貫通孔開口径Rの差を2xとしたとき、x/Rを0.1〜0.3、シリコンウエハとプレートの距離を0.05mm〜1.0mmとしたときに、前記課題を実現できる。プレートは、多孔質セラミックのような絶縁体でかつ多孔質材料が望ましく、シリコンウエハ表面のめっき成長も抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細なコンタクト構造であっても、低コンタクト抵抗のコンタクト構造を形成することができる半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板11の表面部に形成された不純物領域15と、不純物領域15の表面から所定深さにわたって形成された金属シリサイド層16とを備える。シリコン基板11上には層間絶縁膜18が形成され、層間絶縁膜18を貫通して底部が金属シリサイド層16に到達するコンタクトホール19が形成されている。コンタクトホール19は、金属シリサイド層16からなる側壁の面積が、金属シリサイド層16からなる底面の面積よりも大きい開口部になっている。さらに、コンタクトホール19の、金属シリサイド層16からなる側壁および底面に接触するコンタクトプラグ21がコンタクトホール19に埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】アライメントマークの形成に関連する歩留まりの低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】GaN層2及びn型AlGaN層3に、絶縁性基板1の表面まで到達する開口部6を形成する。次に、開口部6内にソース電極4sに接続されるNi層8を導電性エッチングストッパとして形成すると共に、n型AlGaN層3上にアライメントマーク8aを形成する。次に、絶縁性基板1の裏面にフォトレジスト膜を形成し、アライメントマーク8aを基準として、ビア用遮光部及びアライメント用遮光部が設けられたフォトマスクの位置合わせを行う。次に、フォトマスクを用いてフォトレジスト膜からビアホール形成用レジストパターンを形成する。次に、ビアホール形成用レジストパターンを用いて、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを形成する。そして、ビア配線16を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】Ru材料をCu配線のバリアメタル膜として使用した際、CMP時にCu溶出の発生しないCu配線形成方法を提供する。

【解決手段】層間絶縁膜上面の第1のバリアメタル上に形成された第2のバリアメタル膜(Ru膜)を除去する工程(d)と、前記工程(d)の後に、前記第1及び第2のバリアメタル膜上にシード銅(Cu)膜を堆積する工程(e)とを有する。このように、シード銅膜を形成する前に、上面の第2のバリアメタル膜を除去してしまうことにより、この第2のバリアメタル膜と銅との電池効果で、銅がスラリー中に溶出することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

141 - 160 / 405

[ Back to top ]