Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

61 - 80 / 405

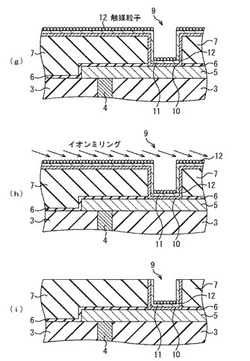

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を内在する炭化珪素半導体を用いても、大面積半導体装置の高歩留りを安定して実現可能な半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体基板上に炭化珪素半導体層をエピタキシャル成長する工程と、炭化珪素半導体層表面を研磨する工程と、研磨する工程の後に、炭化珪素半導体層に不純物をイオン注入する工程と、不純物を活性化するための熱処理をする工程と、熱処理をする工程の後に、炭化珪素半導体層表面に第1の熱酸化膜を形成する工程と、第1の熱酸化膜を化学的に除去する工程と、炭化珪素半導体層上に電極層を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

銅の選択的かつ清浄なエッチングのための集束イオンビームプロセス

集積回路編集のための銅の集束イオンビームエッチング用のエッチング促進剤はイオンビームによる隣接する誘電体の損失を防ぎ、隣接面上のスパッタされ再堆積した銅を非導電性にして電気的短絡を回避する。促進剤は分子中にN−N結合を有し、約70〜220℃の沸点を有し、ヒドラジン及び水の溶液と、ヒドラジン誘導体と、メチル、エチル、プロピル及びブチルから選択された2つの炭化水素基によって飽和したニトロソアミン誘導体と、ニトロソアミン関連化合物と、四酸化窒素とを含み、好適にはヒドラジン一水和物(HMH)、ヒドロキシエチルヒドラジン(HEH)、CEH、BocMH、BocMEH、NDMA、NDEA、NMEA、NMPA、NEPA、NDPA、NMBA、NEBA、NPYR、NPIP、NMOR及びカルムスチン単独、又は四酸化窒素との組合せである。促進剤は高アスペクト比(深さ)の孔の銅をエッチングするのに有効である。  (もっと読む)

(もっと読む)

反射電極、および反射電極を備えた表示デバイス

【課題】高い反射率および低い接触抵抗を有しており、しかも、ヒロックなどの欠陥を生じることのない耐熱性にも優れた反射電極を提供する。

【解決手段】基板1上に形成される表示デバイス用の反射電極2であって、前記反射電極は、0.05〜2原子%のNi及び/又はCo、並びに0.1〜2原子%のNdを含有する第1のAl−(Ni/Co)−Nd合金層2aとAlとO(酸素)を含有する第2のAl酸化物層2bと、を有している。上記Al酸化物層は透明画素電極3と直接接続しており、前記Al酸化物層中のO原子数とAl原子数との比である[O]/[Al]が、0.30以下であり、前記Al酸化物層の最も薄い部分の厚みが、10nm以下である。上記反射電極は、前記Al酸化物層と前記透明画素電極とが直接接続する領域において、前記透明画素電極と前記基板との間に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面側で、Al電極膜表面にボイドが形成され難くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の一方の主面側に半導体機能領域と所要のコンタクトホール8を含む層間絶縁膜7パターンを形成した後、該半導体基板1の前記一方の主面側の全面に、厚膜のアルミニウム膜またはアルミニウム合金膜を成膜して前記コンタクトホール8の底面を含む半導体基板1表面に導電接触させて所要の電極膜9を形成する際に、前記アルミニウムの成膜工程を膜厚に関して複数回に分け、複数回の前記アルミニウム成膜工程の間に、直前のアルミニウム膜表面の凹凸を等方性エッチングにより平坦化する工程を設ける半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ13とを有することを特徴とする。

(もっと読む)

薄膜のパターニング方法、デバイス及びその製造方法

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

アモルファスなタンタル−イリジウム拡散バリアを用いた銅相互接続構造、その形成方法、および該方法による半導体デバイス製造方法

【課題】ライナ/銅界面のボイド生成部位の排除により、高い信頼性および生産歩留まりが得られる半導体デバイス製造方法を提供する。

【解決手段】半導体デバイス製造に用いる拡散バリアを形成する方法は、物理蒸着(PVD)工程によって、パターン形成された中間誘電体(ILD)層の上に、イリジウム・ドープされたタンタル・ベースのバリア層を堆積するステップを含み、該バリア層は、原子量で少なくとも60%のイリジウム濃度で、バリア層が結果としてアモルファス構造を有するように堆積される。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線の微細構造の維持、TDDB寿命の確保および低抵抗を実現する。

【解決手段】半導体装置100は、基板102と、基板102上に形成された層間絶縁膜104と、層間絶縁膜104中に形成された配線120と、を含み、配線120は、断面視において、最上面から下方にかけて幅が広くなる領域を有する。

(もっと読む)

61 - 80 / 405

[ Back to top ]