Fターム[5F033XX13]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 密着性改善 (1,147) | 基板と配線又は配線間の密着性改善 (389)

Fターム[5F033XX13]に分類される特許

41 - 60 / 389

パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板

【課題】パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板を提供する。

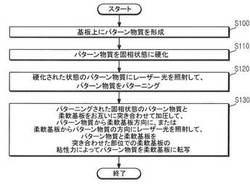

【解決手段】本発明によるパターン転写方法は、基板上にパターン物質を形成する第1段階と、パターン物質を固相状態に硬化させる第2段階と、硬化された固相状態のパターン物質にレーザー光を照射して、パターン物質をパターニングする第3段階と、パターニングされた固相状態のパターン物質と柔軟基板をお互いに突き合わせて加圧して、パターン物質から柔軟基板方向に、または柔軟基板からパターン物質方向にレーザー光を照射して、パターン物質と柔軟基板を突き合わせた部位で発生する柔軟基板の粘性力によって、パターン物質を柔軟基板に転写する第4段階と、を含む。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体デバイス製造方法

【課題】バリア金属膜とCVD法によって形成される金属導体膜である銅膜との間の密着性に優れた半導体デバイスの製造方法を提供すること。

【解決手段】基板上に直接にまたは絶縁体膜を介してバリア金属膜を形成する工程と、該バリア金属膜上にCVD法によって銅膜を形成する工程とを含む半導体デバイス製造方法において、該バリア金属膜を形成する工程と該銅膜を形成する工程との間に、加熱条件下アンモニア、水素、またはシランのうちの少なくともいずれか1つを含む第1の還元性ガスに暴露する工程と、該銅膜を形成する工程の後に、加熱条件下第2の還元性ガスに暴露する工程と、を有することを特徴とする。

(もっと読む)

Co膜形成方法

【課題】膜中及び膜表面の不純物が効果的に除去でき、Cu配線構造に適用したときにバリア層及びCu配線層に対する密着性に優れて一層の低抵抗を実現できるCo膜形成方法を提供する。

【解決手段】基材Sを処理室10内に配置して処理室内を真空引きすると共に、基材を一の所定温度に加熱し、アルキル基を有するイオン又は分子がコバルトに配位した有機金属材料Lを気化させ、気化させた有機金属材料を基材表面に供給し、有機金属材料を熱分解させてCo膜を成膜する。その後、同一の処理室内で、またはCo膜が成膜された基材を他の処理室内に配置し、この基材をアンモニアガスと水素ガスとを含む混合ガス雰囲気中にて他の所定温度でアニールする。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

貫通孔を形成しためっき層付シリコン基板

【解決課題】 複数の微細な貫通孔が存在するシリコン基板において、半導体プロセスに依らない簡素な技術により平坦部のみならず貫通孔内部にも密着性が良好な金属膜を成膜して、高密度実装用途に好適なシリコン基板を提供する。

【解決手段】 めっき前処理によりシリコン基板の平坦部と貫通孔内部の清浄シリコン表面を現出させ、ニッケル置換めっき・無電解銅めっき(S4)を順に行うことにより、シリコン基板の全ての貫通孔の内壁全面ならびに主面の全面もしくは一部の面を直接被覆し、密着性に優れ良好な導電性を示す膜を有するめっき層付シリコン基板を作製することができる。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の銅配線の信頼性をTDDB寿命とEM寿命との双方に関して向上させる。

【解決手段】 半導体装置の配線層30は、配線溝が形成された絶縁膜32、35と、配線溝の内面に形成されたバリアメタル層41と、バリアメタル層41を介して配線溝内に形成された銅配線膜43とを有する。バリアメタル層41は、配線溝の内壁面側から順に形成された第1乃至第3のバリアメタル膜41−1、2、3を有する。第2のバリアメタル膜41−2は、第3のバリアメタル膜41−3側の表面部分において、クラスタイオン照射によって形成された、その他の部分より高い密度の緻密層41−2aを有する。第3のバリアメタル膜41−3は、例えばルテニウム等、銅配線膜43との密着性に優れた材料を有する。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

41 - 60 / 389

[ Back to top ]