Fターム[5F033XX13]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 密着性改善 (1,147) | 基板と配線又は配線間の密着性改善 (389)

Fターム[5F033XX13]に分類される特許

21 - 40 / 389

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理の後も低い電気抵抗率を有する新規なCu合金膜を提供すること。

【解決手段】表示装置用Cu合金膜であって、前記Cu合金膜は、Cu−Mn−B合金で構成されており、前記Cu合金膜の基板側の界面(I)から、前記Cu合金膜の最表面に向って50nm(II)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnI−II)およびB量(BI−II)とすると共に、前記Cu合金膜の深さ50nm(II)から、前記Cu合金膜最表面(III)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnII−III)およびB量(BII−III)とし、前記Mn量のMnI−IIとMnII−IIIとの関係が、2.0≦(MnI−II/MnII−III)であると共に、前記B量のBI−IIとBII−IIIとの関係が、1.5≦(BI−II/BII−III)であること。

(もっと読む)

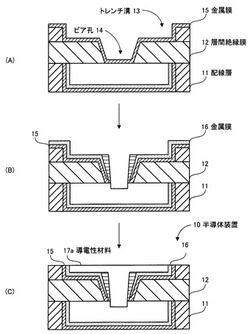

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

パターン修正方法

【課題】配線パターンの修正において、修正抵抗を低減することが可能となる、パターン修正方法を提供する。

【解決手段】パターン修正方法は、導電性パターン20の欠陥部21を修正するパターン修正方法であって、導電性インクを塗布することにより第1のインク層31を形成する工程と、第1のインク層31を焼成することにより第1の修正層32を形成する工程と、少なくとも一部が第1の修正層32に重なるように導電性インクを塗布することにより、第2のインク層33を形成する工程と、第2のインク層33を焼成することにより第2の修正層34を形成する工程とを備え、第1の修正層32および第2の修正層34により欠陥部21を挟んで配置される導電性パターン20間の電気的接続が確保される。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

(もっと読む)

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

半導体装置及びその配線の形成方法

【課題】 密着性を低下させることなく切削性を向上させることが可能な半導体装置及びその配線の形成方法を提供する。

【解決手段】 基板1上に開口部を形成するように絶縁樹脂4を形成する工程と、前記絶縁樹脂4上と、前記開口部の側壁面5aと底面とに第1配線層7を形成する工程と、前記第1配線層7上に第2配線層8を設ける工程と、前記開口部の前記側壁面5a上に形成された前記第1配線層7を露出するように切削して平坦化する工程とを含み、前記第1配線層7を形成する工程では、前記開口部の前記側壁面5aに形成される前記第1配線層7の厚さより前記底面に形成される前記第1配線層7の厚さの方が厚くなるように形成することを特徴としている。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】再配線構造を有する半導体装置において、外部接続電極の接合性の低下、層間剥離、クラックの発生等を抑制して信頼性を向上する。

【解決手段】半導体装置50は、配線層絶縁膜3内に形成された信号配線1と、配線層絶縁膜3上に形成された絶縁膜6及び7と、絶縁膜6及び7内で且つ信号配線1上に形成された配線電極4と、絶縁膜6及び7内で且つ配線電極4上に形成された第1の金属層10aと、絶縁膜6及び7上に形成され、第1の金属層10aの上面に接続された金属配線10cと、金属配線10c上に形成された外部接続電極13aとを備える。更に、絶縁膜6及び7内で且つ外部接続電極13aの下方に形成され、金属配線10cの下面に接続された第2の金属層10bを備える。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

金属薄膜の成膜方法、半導体装置及びその製造方法

【課題】単膜でCu拡散のバリア膜及びめっきシード層として機能するとともに、Cuとの密着性にも優れた金属薄膜の成膜方法を提供する。

【解決手段】金属薄膜の成膜方法は、Ti膜を成膜する工程(STEP1)、Ti膜上にCo膜を形成する工程(STEP2)、Ti膜及びCo膜を熱処理してCo3Ti合金を含む金属薄膜を形成する工程(STEP3)を備えている。Co3Ti合金を含む金属薄膜は、優れた導電性とCu拡散バリア性を有し、Cuとの格子不整合が0.15%と非常に小さいため、Cu配線と優れた密着性が得られる。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体装置及びその製造方法

【課題】銅又は銅合金からなる配線との密着性が高いバリアメタル層を備え、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、半導体基板100の上方に配置された絶縁膜106と、絶縁膜106中の溝に配置され、銅又は銅合金からなる配線115とを備え、絶縁膜106と配線115との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、非晶質構造を有する第1のバリアメタル層109と第1のバリアメタル層109の上に配置された多結晶構造を有する第2のバリアメタル層110からなる積層構造であり、第2のバリアメタル層110には銅が含まれており、第2のバリアメタル層110中の金属に占める銅の割合は50at%以下である。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

金属銅膜の作製方法及び印刷金属銅パターン

【課題】印刷形成が可能である銅系粒子堆積層を、基板密着性、低体積抵抗率、基板ダメージがなく深部まで還元する処理方法であり、且つ印刷塗布部外への銅の析出を抑制した、金属銅膜の作製方法、及び、作製した印刷金属銅パターンを提供する。

【解決手段】基板上に形成された、酸化銅からなる粒子を含む銅系粒子堆積層を、120℃以上において、ガス状のギ酸と、ガス状の1価のアルコール/エステル/ケトンから選択される少なくとも1種の有機溶剤と混合ガスにより処理する、金属銅膜の作製方法。

(もっと読む)

半導体装置

【課題】 半導体素子の電極がはんだバンプを介して接続パッドに電気的に接続されているとともに、エレクトロマイグレーションが効果的に抑制された半導体装置を提供する。

【解決手段】 半導体基板1の電極3の外周の一部に電子回路2が直接に接続されてなる半導体素子と、半導体素子の電極3と対向して配置された接続パッド5を備える配線基板4と、電極3と接続パッド5との間に介在して、電極3および接続パッド5に接合されたはんだバンプ6とを備え、電極3とはんだバンプ6との界面に沿って、電極3の外周の電子回路2が接続されている一部に接した部分において他の部分よりも厚いニッケル層7が介在している半導体装置である。ニッケル層7の厚みの差に応じた電気抵抗差によって、半田バンプ6に流れる電流の電流密度を均一化し、電流の集中によるマイグレーションを抑制できる。

(もっと読む)

Cu合金スパッタリングターゲットおよび半導体装置のCu配線膜の製造方法

【課題】 ガラス基板やSi系膜との密着性に優れ、SiとCuとにおける高い拡散バリア性を有し、尚且つ水素プラズマ雰囲気に曝されても膜の膨れや膜剥がれが発生し難い、下地膜等を得るためのCu合金スパッタリングターゲットおよび半導体装置のCu配線膜の製造方法を提供する。

【解決手段】 本発明は、Ce酸化物を25〜53質量%含有し、残部Cuおよび不可避的不純物からなるCu合金スパッタリングターゲットである。また、本発明は、Ce酸化物を25〜53質量%含有し、残部Cuおよび不可避的不純物からなるCu合金スパッタリングターゲットをスパッタリングして下地膜を形成し、次いで該下地膜上にCu系配線膜をスパッタリングにより形成する半導体装置のCu配線膜の製造方法である。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

21 - 40 / 389

[ Back to top ]