Fターム[5F033XX17]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | クラック防止、歪み防止 (509)

Fターム[5F033XX17]に分類される特許

81 - 100 / 509

半導体基板および半導体基板の製造方法

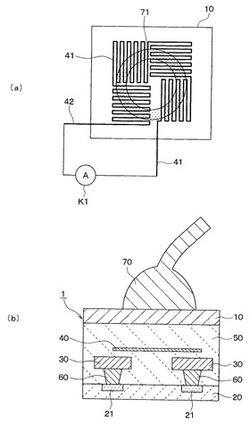

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ウェーハの裏面研削やダイシングの際に生じる、水分の浸入による汚れ、あるいは割れ、クラック、チッピング、層間剥離等の物理的損傷を抑制することを目的とする。

【解決手段】基板11上のチップ領域12の周縁部にその内側の部分を連続して取り囲むよう有機保護膜23’を形成する。また、パッシベーション膜22および有機保護膜23がキャップ層47上に閉環状開口部を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】無機材料を用いてコストの低減を図りながら、応力集中によるクラックを回避しつつ、銅配線を覆うことができるパッシベーション膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10は、層間絶縁膜25と、層間絶縁膜25上に突出して形成され、銅を主成分とする材料からなる配線27と、配線27を覆うように形成されたパッシベーション膜30とを含む。パッシベーション膜30は、配線27側から順に第1窒化膜31、中間膜33および第2窒化膜32を積層した積層膜からなる。中間膜33は、第1および第2窒化膜31,32とは異なる絶縁材料(たとえば酸化物)からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜が剥離しにくい半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法において、複数のデバイス領域がスクライブライン領域によって区画された半導体ウェーハ上に、層間絶縁膜内に配線及びビアが設けられた多層配線膜を形成する工程と、前記スクライブライン領域内に設定されたダイシング領域の一部に配置された前記多層配線膜及び前記半導体ウェーハを除去することにより、前記多層配線膜及び前記半導体ウェーハを前記デバイス領域毎に切り分ける工程と、を設ける。そして、前記多層配線膜を形成する工程において、前記スクライブライン領域における前記ダイシング領域を除く領域には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成し、前記ダイシング領域における前記層間絶縁膜の少なくとも上部には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成しない。

(もっと読む)

半導体装置及びその製造方法

【課題】 膜ストレス低減を図った無機SOG膜を有した半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された下層配線3と、前記下層配線3上及び下層配線3間に形成され、不純物がイオン注入されることで圧縮応力を示す無機SOG膜5aと、前記無機SOG膜5aを含む層間絶縁膜7に形成されたコンタクトホールを介して前記下層配線に接続する上層配線とを具備することを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、及び電子機器

【課題】積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。また、固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】第1の半導体ウェハ31と、第2の半導体ウェハ45とを、基板間配線68で接続する構成とする。基板間配線は、第1の半導体ウェハ31表面の第1の多層配線層に形成される接続孔66と、第2の半導体ウェハ45表面の第2の多層配線層に形成された貫通接続孔65とに、導電材料が埋め込まれて形成されている。そして、貫通接続孔65は接続孔66の直径よりも大きく形成されている。これにより、貫通接続孔65の構内に導電材料を埋め込む際のボイドの発生を防ぐ。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】低誘電率の絶縁膜を備える一方で、当該絶縁膜上に選択的に設けられたキャップ層を備えておらず、信頼性に優れた半導体装置を効率よくかつ確実に製造することができる製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする、ナノインデンターを用いた測定から求められる弾性率が、4.0GPa以上である絶縁膜を形成する工程を有する一方で、絶縁膜上にキャップ層を形成する工程を有していない。

(もっと読む)

半導体集積回路及びその製造方法

【課題】検査時におけるプロービングの機械的な力学的ストレスや、組立のワイヤ・ボンディングによる機械的な力学的ストレスによって発生する応力を緩和できる構成を有する半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンと電気的に接続する第1のバス(140)と、第2の金属パターンと電気的に接続する第2のバス(150)と、第1のバス(140)及び第2のバス(150)に1つづつ設けられたコンタクト・パッド(304)とを備え、第1のバス(140)及び第2のバス(150)の各々には、少なくとも1つのスリット(10a)が形成されている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

半導体装置

【課題】低誘電率誘電体材料などからなる層間絶縁膜を用いた多層配線構造を有する半導体装置において、機械的ストレス又は熱的ストレスに起因する層間絶縁膜のクラック又は剥離等を確実に防止する。

【解決手段】半導体基板のチップ領域の外周部にシールリング4が設けられていると共に、当該チップ領域におけるシールリング4の近傍にチップ強度強化用構造体5が設けられている。チップ強度強化用構造体5は複数のダミー配線構造(例えばダミー配線構造5A〜5E等)から構成されている。各ダミー配線構造5A〜5E等はそれぞれ、最下層及び最上層の配線層のいずれか一方のみを含むか又はいずれも含まない2層以上の配線層に亘ってビア部を介して連続的に形成されている。

(もっと読む)

半導体装置

【課題】ダイシングブレードでダイシングする際の層間絶縁膜間の密着性を良好にしつつ、層間絶縁膜の層間クラックを防ぐ。

【解決手段】スクライブライン領域202において、ダイシング工程においてダイシングブレードが通るブレード領域204およびブレード領域204の両側に形成され、ダイシングブレードが通らない非ブレード領域206にそれぞれダミー配線が形成され、非ブレード領域206においては上下に隣接するダミー配線106bとダミー配線110bとがダミービア108bで接続され、ブレード領域204においては、上下に隣接するダミー配線106aとダミー配線110aとがダミービアで接続されていない。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

半導体装置

【課題】ワイヤボンディング接続されるパッケージに搭載される場合のワイヤ長を短くできる半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、シリコン基板103の内部素子領域153に形成された複数の素子と、シリコン基板103上に形成される配線層120と、配線層120を貫通し、内部素子領域153を囲む環状のシールリング101と、内部素子領域153の上方、かつ、配線層120上に形成され、複数の素子に含まれる第1素子と接続されるパッド102と、シールリング101上に形成され、当該シールリング101と接続されたパッド102aとを備える。また、シールリング101は、複数の素子に含まれる第2素子と接続されている。

(もっと読む)

81 - 100 / 509

[ Back to top ]