Fターム[5F033XX17]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | クラック防止、歪み防止 (509)

Fターム[5F033XX17]に分類される特許

21 - 40 / 509

半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】前記半導体装置をスクライブ工程により切り離す際に、クラックが歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのを抑制し、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記保護溝部の底面の一部及び前記保護溝部の内側の側壁面に連続して形成された保護膜と、を有する。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

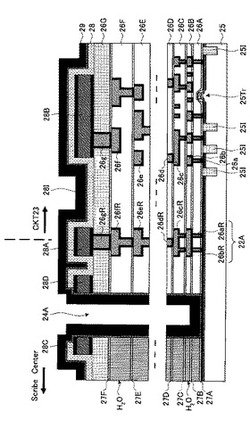

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

半導体装置

【課題】ダイシング時の衝撃を逃がして、半導体装置の歩留まりを向上させる。

【解決手段】半導体装置100は、シリコン層4上に形成された多層配線構造3内で、平面視において素子形成領域50の外周に形成されたシールリング6と、シールリング6のさらに外周に形成されたダミーメタル構造30a〜ダミーメタル構造30iを含む。ダミーメタル配線24は、内周側に形成されたものほど上層に配置される。

(もっと読む)

半導体装置の製造方法、半導体装置、及びこれらの層間絶縁層の形成に用いる溶液

【課題】配線間の間隙又は配線の下面と基板の上面との間隙に、絶縁膜を埋設することが困難であった。

【解決手段】半導体装置100の製造方法は、次の工程を含む。すなわち、基板上に絶縁層(絶縁層106)を形成する工程。絶縁層106の一部を選択的に除去して凹部(配線溝107及び配線溝110)を形成し、当該凹部内にバリアメタル膜112と金属膜114とをこの順で埋め込むことにより配線(配線115a、115b)を形成する工程。配線(配線115a、115b)を残しつつ、絶縁層106を除去する工程。絶縁層106を除去する前記工程後、下記の溶液を用いて、配線(配線115a、115b)の周囲を埋設する層間絶縁層118を形成する工程。溶液は、シラン化合物と、界面活性剤からなるポロジェンと、シラン化合物の溶質濃度の増加に応じて、アルコールと比較して、シラン化合物を表面に析出させやすく、かつ増粘しにくいシーター溶媒(アルコール及び水を除く)と、を含むことにより特定される。

(もっと読む)

イメージセンサ構造体、イメージセンサの製造方法およびイメージセンサ

【課題】イメージセンサのカラーフィルターの膜厚のばらつきを低減する。

【解決手段】イメージセンサ構造体は、シリコン基板51上に配列で形成された複数のイメージセンサと、複数のイメージセンサをダイシングして分離するときに切断される、隣り合うイメージセンサの間のスクライブラインと、から構成される。複数のイメージセンサのそれぞれは、シリコン基板51上に形成された拡散層52から構成される複数の光電変換素子と、複数の光電変換素子を囲んで、イメージセンサそれぞれの外周に沿って導体で形成されたガード配線81と、を備える。そして、スクライブライン部53に、ガード配線81と同一のプロセスで同層に形成されたダミー配線82が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 薄板化の際に層間絶縁膜が破損することを抑制できる半導体装置を得る。

【解決手段】 第1の硬度を有する材料で構成された基板10と、基板10の第1主面10aに設けられたドリフト層11と、ドリフト層11上に絶縁膜60を介して形成されたゲート電極70と、ゲート電極70を覆うように形成され、第1の硬度よりも小さい第2の硬度を有する材料で構成された層間絶縁膜80とを備え、基板10とドリフト層11とを合わせた厚みは200μm以下であり、層間絶縁膜80に、平面視において、全ての内角が90°より大きい多角形、円形または楕円形の開口90が設けられている半導体装置。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

21 - 40 / 509

[ Back to top ]