Fターム[5F033XX17]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | クラック防止、歪み防止 (509)

Fターム[5F033XX17]に分類される特許

141 - 160 / 509

半導体装置とその製造方法

【課題】表面電極にはんだ接合層を有する半導体装置において、その製造工程でウェハの反りやはんだ接合層のクラックが発生することを抑制する。

【解決手段】表面電極は、半導体基板に接する第1層として250℃以下の基板温度でスパッタ法によってAl−Si層またはAl−Si−Cu層を形成し、その表面に積層する第2層として400℃以上の基板温度でスパッタ法によってAl層またはAl−Cu層を形成し、その表面側に、はんだ接合層、はんだ層を形成することによって、製造する。

250℃以下の基板温度で第1層を形成するため、シリコンノジュールの発生を防止することができ、第2層を400℃以上の基板温度で形成するため、第2層の平坦性を確保でき、ウェハの反りやはんだ接合層のクラック発生を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部からの水分がパッド上の開口部に浸入した場合でも、開口部の側面に露出している窒化チタン膜が酸化チタン膜に変化することを抑制することができ、半導体装置の信頼性を向上できる技術を提供する。また、パッドの表面保護膜にクラックが発生することを抑制し、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】開口部OP2の径を開口部OP1の径よりも小さくし、かつ、開口部OP2を開口部OP1に内包されるように形成する。これにより、開口部OP1の側面に露出する反射防止膜ARの側面を、開口部OP2を形成している表面保護膜PAS2で覆うことができる。この結果、反射防止膜ARの側面を露出することなく、パッドPDを形成することができる。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

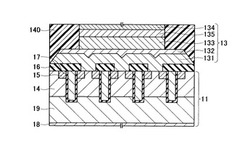

配線層レイアウト方法及び半導体装置

【課題】配線層にスリットを設けたり、下層に位置する配線層にライン幅及びスペース間隔の比率を制限したりすることなく、SOG膜を含む層間絶縁膜におけるクラックの発生を防止する。

【解決手段】下地絶縁膜3上に第1配線層5が形成されている。下地絶縁膜3上及び第1配線層5上に第1層間絶縁膜7が形成されている。回転塗布法及びエッチバック処理により第1層間絶縁膜7上に第2層間絶縁膜9が形成されている。第1層間絶縁膜7上及び第2層間絶縁膜9上に第3層間絶縁膜11が形成されている。第3層間絶縁膜11上に第2配線層13が形成されている。第1配線層5のうち幅寸法が10.0μm以上の幅広第1配線層5に対して、第2配線層13のうち幅寸法が10.0μm以上の幅広第2配線層13は、上方から見て、幅広第1配線層5と1.0μm以上の重なりをもって配置されているか、幅広第1配線層5とは2.0μm以上の間隔を設けて配置されている。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】現在のLSI、すなわち、半導体集積回路装置の製造工程においては、デバイスの組み立て(たとえばレジン封止)後に、高温(たとえば摂氏85から130度程度)・高湿(たとえば湿度80%程度)の環境下での電圧印加試験(すなわち、高温・高湿試験)が広く行われている。これに関して、高温・高湿試験中に、正電圧が印加されるアルミニウム系ボンディング・パッドの上面端部において、封止レジン等を通して侵入した水分に起因する電気化学反応により、反射防止膜である窒化チタン膜が酸化されて膨張し、上部膜との剥がれや、膜クラックが発生することが、本願発明者等によって明らかにされた。

【解決手段】本願発明は、アルミニウム系ボンディング・パッドの周辺部において、パッド上の窒化チタン膜をリング・スリット状に除去するものである。

(もっと読む)

半導体装置

【課題】小型化・高耐圧化に優れ信頼性の高いパワー半導体装置を生産効率良くかつ高い製品歩留まりで製造できる誘電体分離型の半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板内のチップ配列領域において格子状のスクライブ領域によって区画された複数のチップ領域が整列配置され、前記複数のチップ領域の各々に半導体素子が形成された誘電体分離型の半導体装置であって、少なくとも前記複数のチップ領域の上には電極配線膜が厚さ0.8μm以上2.3μm以下で形成されており、前記電極配線膜の上に前記電極配線膜を保護するパシベーション膜が厚さ0.8μm以上2.7μm以下で形成されており、前記電極配線膜の厚さに対する前記パシベーション膜の厚さの比率が1.0以上1.2以下であることを特徴とする。

(もっと読む)

表示装置用Al合金膜、表示装置および該表示装置の製造方法、ならびにAl合金スパッタリングターゲット

【課題】表示装置(LCD)におけるパネルのTAB部引き出し電極の断線を防止することができ、かつ、バリアメタル層を介在させずにAl合金膜を透明画素電極と直接接続することのできるAl合金膜を提供する。

【解決手段】表示装置に用いられるAl合金膜であって、NiおよびCoよりなる群から選択される少なくとも1種の元素(X元素)を0.1〜2.0原子%含み、長径0.01μm超であってNi量とCo量の合計が10原子%以上である化合物が、100μm2あたり3個超析出していると共に、Al結晶粒内の固溶Ni量と固溶Co量の合計が0.1〜0.5原子%であり、かつ、Al合金膜の硬度が1.5GPa以上3.0GPa以下であるところに特徴を有する表示装置用Al合金膜。

(もっと読む)

アモルファススピンオングラス膜の形成方法

【課題】基板の温度を低温に保ってSOG膜をキュア処理することができ、かつキュア処理時の膜のクラックの発生を低減させることが可能なSOG膜の形成方法を提供する。

【解決手段】シリコン及び/又はシリコン化合物と有機溶媒を含有するスピンオングラス材料を基板に塗布した後に、酸素を主成分とするガスにより形成されたプラズマ中で結晶化が生じない条件下で、前記スピンオングラス材料塗膜を高密度化することによりアモルファススピンオングラス膜を形成する。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板の側面下端のエッジ部を保護し、且つ、装置全体を薄型化する。

【解決手段】 シリコン基板1の側面に形成された円弧状に凹んだ傾斜面13にはアモルファスシリコンやポリイミド系樹脂等からなる側部保護膜14が設けられている。これにより、シリコン基板1の側面下端のエッジ部1aを保護することができる。この場合、側部保護膜14の下端部下面はシリコン基板1の下面と面一となっているので、シリコン基板1の下面に樹脂保護膜を形成する場合と比較して、薄型化することができる。

(もっと読む)

半導体装置

【課題】ダイカット時に回路素子領域に近い箇所でクラックが発生することを防止する。

【解決手段】半導体基板100上に形成された回路素子領域と、前記回路素子領域を囲むように形成されたダイカット領域と、前記回路素子領域とダイカット領域との間の少なくとも一部に形成された保護パターンと、を備え、前記保護パターンは、前記半導体基板の表面部に形成された素子分離領域102と、素子分離領域102よりダイカット領域側に形成され、素子分離領域102より幅の狭い素子分離領域103と、素子分離領域102と素子分離領域103との間に形成された素子領域150と、素子分離領域102上に形成されたゲート層106と、ゲート層106上に層間絶縁膜111を介して形成された配線層113と、前記配線層113上に形成されたパッシベーション層120と、素子分離領域103のダイカット領域側に隣接して形成されたゲート層107と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドよりも径の小さな貫通孔を半導体基板自体に設けることなく、上下に積層された半導体チップ間の電気的な接続を行う。

【解決手段】半導体基板S1の横にはみ出すように電極パッドP1を配置し、半導体基板S1の周囲を取り囲むように配置された樹脂層J1上にて支持し、電極パッドP1が上下に重なるように半導体チップC1を積層し、貫通孔T1内に導電体D1を埋め込むことで、上下の電極パッドP1を電気的に接続し、上下に積層された半導体チップC1間の電気的な接続を行う。

(もっと読む)

半導体装置

【課題】 半導体素子のサイズを大きくすることなく、プロービング試験の際にボンディング領域に針跡が到達していないかどうかを容易に確認することができる構造を備えた半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上に設けられた第1の金属層26と、前記第1の金属層26上に設けられた絶縁層30と、前記絶縁層30上に設けられ、外部に露出した電極パッド面33a、33bを有する第2の金属層33と、を含み、前記第2の金属層33及び前記絶縁層30に、凹部31が形成されており、前記絶縁層30の前記凹部31内に、前記第2の金属層33が設けられていることを特徴とする。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】シールリングの構造を最適化して、ダイシング部の切断面からの水分の侵入やクラックの伸展に対する障壁としての機能を確保したシールリングを備えた半導体装置の製造方法を提供する。

【解決手段】半導体基板1上の回路形成領域とダイシング領域との間にシールリング100が配設されている。シールリング100は、断面形状がT字型をなすシール層が積層された部分と、断面形状が矩形をなすシール層が積層された部分とを有している。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】フリップチップ実装構造の半導体装置では、半導体基板(半導体チップ)裏面に抵抗を低減するための厚い金属層が設けられる。しかし、半導体チップの薄化が進むと、厚い金属層との応力の差により、半導体基板に反りが発生し、歩留まりが悪化する原因となっていた。

【解決手段】第1主面に動作領域が設けられ、第2主面に金属層が設けられる半導体基板(半導体チップ)の、少なくとも動作領域と一部重畳する第2主面側の半導体基板に凹部を設ける。これにより周辺部において第1の厚みを有し、凹部において第1の厚みより薄化された第2の厚みを有する半導体チップとする。周辺部が第1の厚みを有するため、第2主面側に厚い金属層を形成しても、半導体チップの反りを防止できる。

(もっと読む)

ディールス・アルダー反応付加部を有する化合物

【課題】半導体素デバイスなどにおける層間絶縁膜用の材料として使用するのに適し、硬膜時における膜減りが小さく、かつ誘電率に優れた膜を製造することができる化合物、およびその化合物を含む組成物、さらにはその組成物より得られる膜を提供。

【解決手段】化合物は、ジエノフィル構造を有する化合物(A)と、環状もしくは直鎖状のいずれかで表される共役ジエン構造を有する化合物(B)とのディールス・アルダー反応により形成され、加熱、光照射、放射線照射またはそれらの組み合わせにより逆ディールス・アルダー反応を介して前記共役ジエン構造を有する化合物(B)を放出する化合物である。

(もっと読む)

半導体装置及びその製造方法

【課題】 銅配線上に銅ワイヤがワイヤボンディングされて構成される半導体装置において、配線剥がれや銅ワイヤ下の絶縁膜にクラックが入るといった不具合を抑止する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された銅配線8と、前記銅配線8の表面及び側面を覆うように形成されたメッキ層10と、前記メッキ層10を介して前記銅配線8上にワイヤボンディングされた銅ワイヤ11とを具備することを特徴とする。

(もっと読む)

141 - 160 / 509

[ Back to top ]