Fターム[5F083GA01]の内容

Fターム[5F083GA01]の下位に属するFターム

Fターム[5F083GA01]に分類される特許

61 - 80 / 981

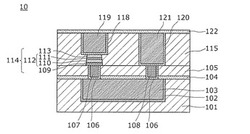

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

記憶装置

【課題】

高速にデータを記録再生することが可能な記憶装置を提供する。

【解決手段】

実施形態の記憶装置は、複数の領域を有し、前記領域に信号を記憶する記憶媒体と、前記記憶媒体に対向する電極を有し、前記電極を介して、それぞれの前記領域に対して信号の書き込みまたは読み出しを行う複数のプローブとを備え、前記複数のプローブは、第1プローブと、前記第1プローブと第1方向に離間して配置する第2プローブと、前記第1プローブに対して前記第1方向及び前記第1方向とは異なる第2方向にそれぞれずらして配置する第3プローブとを含む記憶装置。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、交互に積層して設けられた複数の電極膜及び層間絶縁膜を有した積層体と、前記積層体を積層方向に貫く半導体ピラーと、前記半導体ピラーと前記電極膜との間に設けられた電荷蓄積膜と、前記半導体ピラーの側面に設けられた添加部と、を備えている。そして、前記半導体ピラーは、ゲルマニウムを含む半導体材料を用いて形成され、前記添加部は、酸化アルミニウムを用いて形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の書き込み特性を向上させることができる。また、不揮発性半導体記憶装置の隣接素子間の干渉を抑制することができる。

【解決手段】本発明の不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面内に、チャネル領域を挟んで互いに離間して設けられたソース領域及びドレイン領域と、前記チャネル領域上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた絶縁性電荷蓄積層と、前記絶縁性電荷蓄積層上に設けられた両側部に絶縁層が設けられた導電性電荷蓄積層と、前記導電性電荷蓄積層上に設けられた層間絶縁膜と、前記層間絶縁膜上に設けられた制御ゲートとを備えている。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

相変化メモリ及びその製造方法

【課題】相変化記録材料から熱を急速に拡散させるための構造を有する相変化メモリとその製造方法を提供する。

【解決手段】層間絶縁膜(10、20、30)内に設けられた複数の導電プラグ(12、14)と、複数の導電プラグの夫々に接して設けられた相変化記録材料膜(16)と、相変化記録材料膜に接して設けられた上部電極(18)と、複数の導電プラグに接しないように導電プラグの側面領域に設けられた放熱のための金属材料部(22)と、を有する相変化メモリ。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体パッケージ

【課題】系統毎の配線長の違いを抑制し、高速動作を実現できる半導体パッケージを提供すること。

【解決手段】第1主面と、第1主面に対向した第2主面とを有する矩形の基板と、第1主面上に実装される第1の半導体チップと、第1の半導体チップ上に積層される1以上の第2の半導体チップと、1以上の第2の半導体チップ上に積層される1以上の第3の半導体チップと、を備え、基板は、第1主面上の第1の辺側に、1以上の第2の半導体チップの電極と接続される第1の接続端子と、第1の接続端子と電気的に接続され、第1の半導体チップの第1の電極と接続される第3の接続端子と、を有し、第1主面上の第1の半導体チップを挟んで第1の辺と対向する第2の辺側に、1以上の第3の半導体チップの第2の電極と接続される第2の接続端子と、第2の接続端子と電気的に接続され、第1の半導体チップの電極と接続される第4の接続端子と、を有する。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

半導体記憶装置

【課題】十分な消去速度が得られる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、前記第1の積層体上に設けられ、選択ゲートとその上に設けられた第2の絶縁層とを有する第2の積層体と、前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、前記第1のホールと連通し、前記第2の積層体を積層方向に貫通して形成された第2のホールの側壁に設けられたゲート絶縁膜と、前記メモリ膜の内側および前記ゲート絶縁膜の内側に設けられたチャネルボディと、を備えている。そして、前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成され、前記チャネルボディの前記選択ゲートの上端近傍に位置する領域は、シリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

メモリ装置

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

61 - 80 / 981

[ Back to top ]