Fターム[5F083GA01]の内容

Fターム[5F083GA01]の下位に属するFターム

Fターム[5F083GA01]に分類される特許

81 - 100 / 981

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置の作製方法

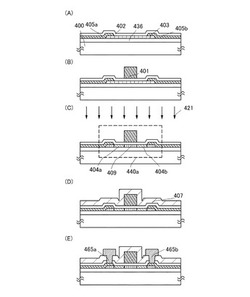

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

強誘電体膜の作製方法

【課題】 良好な規格化保持時間を有するエピタキシャル成長させて得られた強誘電体膜の作製方法を提供すること。

【解決手段】 チタン酸ストロンチウム単結晶基板又はシリコン単結晶基板上に、電極層を介して、強誘電体膜をエピタキシャル成長させて形成し、次いでエピタキシャル成長させて形成された強誘電体膜を冷却する強誘電体膜の作製方法において、この冷却を、少なくとも冷却を開始した後から該強誘電体のキュリー温度より15%高い温度〜15%低い温度の範囲までの冷却速度をその範囲の温度から室温までの冷却速度より遅くして実施する第1冷却工程と、次いで該第1冷却工程の冷却速度より早い冷却速度で室温まで冷却する第2冷却工程とで実施する。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】書き込み特性を向上することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】複数のゲート電極構造13は、半導体基板11上に形成されたゲート絶縁膜12、電荷蓄積層14、ゲート間絶縁膜15、第1制御ゲート16、及び前記第1制御ゲートより幅が広い第2制御ゲート電極17を有する。絶縁膜19は、制御ゲート電極17間及び制御ゲート電極より上方に形成された空隙19を有する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

セルダイオードを採用する相変移記憶素子及びその製造方法

【課題】セルダイオードを用いる相変移記憶素子及びその製造方法を提供すること。

【解決手段】相変移記憶素子は、第1導電型の半導体基板及び前記半導体基板上に配置された複数のワードラインを備える。前記ワードラインは、前記第1導電型と異なる第2導電型を有して実質的に平らな上部面を有する。前記ワードラインのそれぞれの上部面上に前記ワードラインの長さ方向に沿って一次元的に配列された第1半導体パターンを提供する。前記第1半導体パターンは、前記第1導電型または前記第2導電型を有する。前記第1半導体パターン上に前記第1導電型を有する第2半導体パターンが積層される。前記ワードライン間のギャップ領域、前記第1半導体パターン間のギャップ領域、及び前記第2半導体パターン間のギャップ領域は絶縁膜で埋められる。前記絶縁膜の上部に複数の相変移物質パターンが二次元的に配列される。前記相変移物質パターンは前記第2半導体パターンにそれぞれ電気的に接続される。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

81 - 100 / 981

[ Back to top ]