Fターム[5F102GD04]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421)

Fターム[5F102GD04]の下位に属するFターム

ヘテロゲート (33)

Fターム[5F102GD04]に分類される特許

21 - 40 / 388

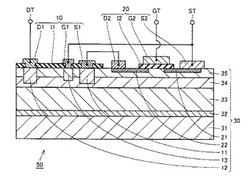

炭化珪素半導体装置

【課題】オン抵抗が低く高速動作が可能でありノーマリオフ特性を有し、かつ一の基板を用いて構成された炭化珪素半導体装置を提供する。

【解決手段】第1、第2、第4および第5不純物領域11、12、21、22は第1導電型を有し、第3不純物領域13は第2導電型を有する。第1〜第3不純物領域11〜13は第1導電型の第1層34に達する。第4および第5不純物領域21、22は第2層35上に設けられている。第1〜第5電極S1、D1、G1、S2、D2は第1〜第5不純物領域のそれぞれの上に設けられている。第1および第5電極S1、D2の間と、第3および第4電極G1、S2の間とは電気的に接続されている。第4および第5不純物領域21、22の間を覆うゲート絶縁膜I2上に第6電極G2が設けられている。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

スイッチ装置

【課題】スイッチ素子のオン抵抗をより一層小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ素子10は、半導体基板104に絶縁膜15を介して接合された電界印加電極14を有している。駆動回路20の電界制御部22は、スイッチ素子10の電界印加電極14およびソース電極13に接続されており、電界印加電極14−ソース電極13間にバイアス電圧Veを印加する。電界制御部22は、閾値を超えるバイアス電圧Veをスイッチ素子10に印加することによって、電界印加電極14から半導体基板104のヘテロ接合界面に電界を印加する。要するに、スイッチ素子10がオン状態で、電界印加電極14から半導体基板104に印加される電界は、電界効果によってチャネル領域の電子濃度を高くし、スイッチ素子10のオン抵抗を小さくするように作用する。

(もっと読む)

半導体装置及びその駆動方法

【課題】順方向電圧降下の平均値を低減し、整流素子の低損失化を実現する半導体装置とその駆動方法を提供する。

【解決手段】アノード電極9とカソード電極3との間に、p型層7と、i層1と、n型層2とを順に形成したダイオード構造の半導体装置において、アノード電極9側に、p型層7と並列に第2n型層8を形成し、順方向バイアス中に、アノード電極9側をp型層7と第2n型層8のいずれかに切り替えるゲート駆動回路10を備えた半導体装置。ゲート電極5は、p型層7と第2p型層6と第2n型層8に接するトレンチ構造4とし、トレンチ内部に絶縁膜4aと電極とを備えたものとすることができる。このゲート電極5は、ゲート駆動回路10から印加するゲート電圧に応じてp型及びn型のチャネルをトレンチ表面に形成する。

(もっと読む)

電動機駆動装置

【課題】装置全体としての長寿命化を図りつつ、装置全体としての小型化を可能とする電動機駆動装置を提供する。

【解決手段】駆動部12は、横型半導体素子からなる1回路2接点式の切替素子16,17を2つ有している。第1の切替素子16は、コモン端子160を電動機11に接続し、第1の端子161および第2の端子162を電源部15に接続する。第2の切替素子17は、コモン端子170を電動機11に接続し、第1の端子171および第2の端子172を電源部15に接続する。制御部14は、各切替素子16,17において、コモン端子160,170が、第1の端子161,171および第2の端子162,172に対して択一的に接続されるように、各切替素子16,17を個別に切替制御する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

21 - 40 / 388

[ Back to top ]