Fターム[5F102GD04]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421)

Fターム[5F102GD04]の下位に属するFターム

ヘテロゲート (33)

Fターム[5F102GD04]に分類される特許

41 - 60 / 388

炭化珪素半導体装置の製造方法

【課題】Al原子を有するコンタクト電極が用いられる場合に、絶縁膜の絶縁信頼性を向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板面12Bを有する炭化珪素基板10が準備される。基板面12Bの一部を覆うように絶縁膜15が形成される。絶縁膜15に接触するように基板面上にコンタクト電極16が形成される。コンタクト電極16はAl、TiおよびSi原子を含有する。コンタクト電極16は、Si原子およびTi原子の少なくともいずれかと、Al原子とを含有する合金から作られた合金膜50を含む。炭化珪素基板10とコンタクト電極16とがオーミックに接続されるようにコンタクト電極16がアニールされる。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

起動回路、スイッチング電源用IC及びスイッチング電源装置

【課題】起動回路を構成するJFETのピンチオフ維持のために生じる電力損失を低減できる起動回路、スイッチング電源用IC及びスイッチング電源装置を提供する。

【解決手段】起動電源(電源コンデンサ)と平滑コンデンサによる補助電源との間に接続され、起動電源による起動電流を平滑コンデンサに流すMOSFETと、ドレイン端子がMOSFETのドレイン端子に接続され、ソース端子が抵抗を介してMOSFETのゲート端子に接続されたJFETと、起動時にJFETのピンチオフ電圧が第1基準電圧値となるように制御し、起動後にJFETのピンチオフ電圧が第1基準電圧値未満の値である第2基準電圧値となるように制御するピンチオフ電圧制御部(可変電圧源)とを備える。

(もっと読む)

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

高分子化合物、これを含む薄膜及びインク組成物

【課題】高い電荷の移動度が得られる高分子化合物を提供すること。

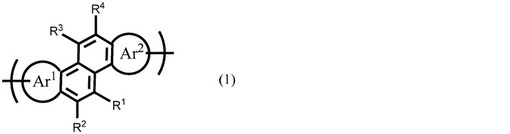

【解決手段】式(1)で表される繰り返し単位を有する高分子化合物。

[Ar1及びAr2は、芳香族炭化水素環、複素環、又は芳香族炭化水素環と複素環との縮合環である。R1、R2、R3及びR4は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、置換シリル基、非置換若しくは置換のカルボキシル基、1価の複素環基、シアノ基又はフッ素原子を示す。]

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

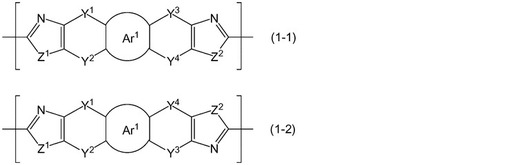

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体8をドライエッチングして形成した平坦表面に電極を形成してもオーミック接触させることができない。

【解決手段】p型III族窒化物半導体8の電極形成範囲をドライエッチングして溝8dを形成し、その溝8dに金属20を充填して電極を形成する。p型III族窒化物半導体8のドライエッチング面は、エッチングによって生じた欠陥によってn型化しているために、平坦平面にドライエッチングしておいて電極を形成するとオーミック接触しない。溝8dを設けておくと、欠陥が少ない溝8dの側面においてp型III族窒化物半導体8と電極がオーミック接触し、半導体と電極の接触抵抗が低減する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体装置

【課題】J−FETのピンチオフ電圧のばらつき低減を図ること、及び低いピンチオフ電圧の実現を図ることが課題となる。

【解決手段】P型半導体基板5上にN型エピタキシャル層6を堆積する。前記N型エピタキシャル層6の表面にN+型ソース層3を形成する。前記N型エピタキシャル層6の表面に前記N+型ソース層3を取り囲んで1対のP+型ゲート層2a、2bを形成する。前記P+型ゲート層2bから離間した領域の前記N型エピタキシャル層6の表面にN+型ドレイン層1を形成する。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

GaNベースの薄膜トランジスタの製造方法

【課題】電流特性と信頼性に優れ、閾値電圧が高いGaNベースの薄膜トランジスタを得ることができる製造方法を提供する。

【解決手段】GaNベースの薄膜トランジスタの製造方法は、n型GaNベースの半導体材を有する半導体エピタキシャル層を、基板上に形成する工程と、半導体エピタキシャル層上に絶縁体層を形成する工程と、絶縁体層上に、絶縁体層を部分的に露出するための開口部を有しているイオン注入マスクを形成する工程と、p型不純物を、開口部および絶縁体層を通してイオン注入して、n型GaNベースの半導体材の中にp型不純物がドーピングされた領域を形成し、その後、絶縁体層およびイオン注入マスクを除去する工程と、半導体エピタキシャル層上に誘電体層を形成する工程と、誘電体層を部分的に除去する工程と、ソース電極およびドレイン電極を形成する工程と、ゲート電極を形成する工程を含む。

(もっと読む)

半導体装置

【課題】化合物半導体上のp型チャネルFETにおいてオン抵抗を低くすることの可能な半導体装置を提供する。

【解決手段】化合物半導体からなる基板10上に、n型チャネルFET領域2とp型チャネルFET領域3とが併設されている。p型チャネルFET領域3において、チャネル層16の下面に接するバッファ層15が、チャネル層16よりも広いバンドギャップを有する第2バッファ層15Bだけで構成された単層構造となっている。さらに、第2バッファ層15Bは、チャネル層16と電子走行層13との間に設けられている。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】低オン抵抗の電界効果トランジスタを低コストで実現する。

【解決手段】電界効果トランジスタは、第一導電型の半導体基体であるN+型SiC基板2及びN-型ドレイン領域1と、N+型SiC基板2の第一主面側に、P型ウエル領域3とN+型ソース領域5とゲート電極7とを有する。N-型ドレイン領域1中に、N-型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面から第二主面へ向かって伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。ゲート電極7直下にチャネル領域が形成されないときに、N-型ドレイン領域1がヘテロ半導体領域4と接することによりN-型ドレイン領域1の全域が空乏化される。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

窒化物系半導体装置

【課題】導通抵抗が低く、かつ高い電圧を維持すると共に、ゲート絶縁膜の破壊を抑制したゲート信頼性の高い窒化物系半導体装置を提供することを目的とする。

【解決手段】AlGaN層20上に形成されたショットキー電極22が、正孔をソース電極30に流す(輸送する)ため、ゲート絶縁膜24、特にトレンチ部23のコーナー部に集中して電圧が印加されることがなくなる。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

41 - 60 / 388

[ Back to top ]