Fターム[5F102GD04]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421)

Fターム[5F102GD04]の下位に属するFターム

ヘテロゲート (33)

Fターム[5F102GD04]に分類される特許

61 - 80 / 388

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

スイッチ装置

【課題】トランジスタのチャネル部の異常を簡易且つ正確に検出できるスイッチ装置を提供する。

【解決手段】複数の半導体層で形成されて、ゲート電極にゲート電圧を印加されることによってドレイン電極−ソース電極間が導通し、ゲート電圧によって半導体層内で正孔と電子とが結合して発光する電界効果トランジスタ11,12と、ゲート電圧を制御する駆動部21と、トランジスタ11,12の発光量を検出する光検出部231,232とを備え、駆動部21は、光検出部231,232の検出結果に基づいて、トランジスタ11,12の異常を判定し、この判定結果に基づいてゲート電圧を制御する。

(もっと読む)

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

半導体装置

【課題】GaN系半導体層のグレインサイズを大型化することが可能な半導体装置を提供すること。

【解決手段】本発明は、(111)面から0.1度以下のオフ角度で傾斜した面を主面とするSi基板10と、Si基板10の主面に接して設けられ、(002)面のX線回折におけるロッキングカーブの半値幅が2000sec以下であるAlN層12と、AlN層12上に設けられたGaN系半導体層20と、を備える半導体装置100である。

(もっと読む)

炭化珪素トランジスタ装置の製造方法

【課題】微細化と、オン特性を改善する、炭化珪素トランジスタ装置の製造方法の提供。

【解決手段】高濃度n型炭化珪素基板2上に、低濃度n型ドリフト層3と高濃度p型層10をエピタキシャル成長する工程と、高濃度p型層10の一部を除去離間した複数の高濃度p型ゲート領域4を形成する工程と、互いに隣り合った高濃度p型ゲート領域4の間に位置するチャネル領域7、高濃度p型ゲート領域4及びゲート電極領域10の全面を覆う低濃度n型ドリフト層3よりも低い不純物濃度の低濃度n型領域11をエピタキシャル成長する工程と、低濃度n型領域11の一部を除去する工程と、低濃度n型領域11の表面にイオン注入し高濃度n型ソース領域5を形成する工程と、高濃度n型ソース領域5上にソース電極6を、高濃度n型炭化珪素基板2の裏面にドレイン電極1を、ゲート電極領域10にゲート電極8を形成する工程を含む炭化珪素トランジスタ装置の製造方法。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

縦型AlGaN/GaN−HEMTおよびその製造方法

【課題】確実なノーマリオフ動作する縦型AlGaN/GaN-HEMTおよびその製造方法を提供する。

【解決手段】n+-GaN基板11の表面にn-GaNバッファ層12、UID-GaN層13、UID-AlGaN層14が順次積層され、UID-AlGaN層の表面に形成されたSiN表面保護膜16と、この表面保護膜の開口部を覆うSiN第1ゲート絶縁膜18と、アパーチャ形成用リセス19内に埋め込まれたn-GaNアパーチャ20と、このアパーチャのn+-GaN基板とは反対側表面と第1ゲート絶縁膜とを少なくとも覆うSiN第2ゲート絶縁膜21と、第1ゲートリセス内の第2ゲート絶縁膜の表面に形成されたゲート電極22と、第1ゲートリセスを挟み、UID-AlGaN層の表面に離間して形成されたソース電極23と、n+-GaN基板のUID-AlGaN層とは反対側の表面に形成されたドレイン電極24とを備える。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体デバイスおよび方法

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の半導体装置は、nチャネルの高電子移動度トランジスタ(HEMT)とpチャネル電界効果トランジスタとを単一の基板上に形成した。

【解決手段】nチャネル電界効果トランジスタは、第1チャネル層7と、この第1チャネル層7にヘテロ接合し、n型の電荷を供給するn型第1障壁層6と、n型第1障壁層6に対してpn接合型の電位障壁を有するp型ゲート領域10とを備え、pチャネル電界効果トランジスタは、p型の第2チャネル層13と、pn接合型の電位障壁を有するn型ゲート領域18とを備える。各トランジスタはpn接合型のゲート領域を有するのでターンオン電圧を高くすることが可能となり、ゲート逆方向リーク電流を減少させたエンハンスメントモードでの動作を実現した。

(もっと読む)

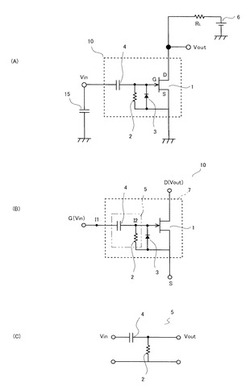

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

双方向スイッチのゲート駆動方法およびそれを用いた電力変換装置

【課題】インバータ等に適用される半導体デバイスとして双方向デバイスを適用した場合に、意図しない過渡期における各部の過電流や過電圧の発生を未然に防止して、低損失なゲート駆動方法を提供することを目的としている。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、双方向にオフ状態から双方向にオン状態へと移行する際に、直接移行しないように制御する制御手段を備え、双方向にダイオードを介在させない動作モードで主として動作し、過渡期においてはダイオードを介する動作が可能なため、低損失かつ各部の過電圧、過電流を防止できる効果が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

コンプリメンタリー接合電界効果トランジスタを備えた炭化珪素半導体装置およびその製造方法

【課題】平坦面に対してデバイス形成できる絶縁分離構造を有し、かつ、高周波でのノイズ伝播や高温時でのリーク電流の発生を抑制できるCJFETを備えたSiC半導体装置を提供する。

【解決手段】絶縁分離層3にてn-型SiC層2やp-型SiC層4を絶縁分離する。これにより、平坦面に対してデバイス形成を行うことができる。このため、製造工程の簡略化を図ることが可能となる。また、PN分離ではなく、半絶縁性のイントリンシック層にて構成された絶縁分離層3によって絶縁分離構造を構成しているため、絶縁分離層3によって高周波ノイズを吸収することによる高周波でのノイズ伝播の抑制を行えると共に、高温時でのリーク電流の発生の抑制を行うことが可能となる。

(もっと読む)

61 - 80 / 388

[ Back to top ]