Fターム[5F140BF27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 高融点金属 (221)

Fターム[5F140BF27]に分類される特許

41 - 60 / 221

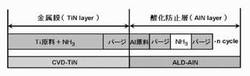

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 金属膜の酸化に起因する特性劣化を最小限に抑えることができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内に処理ガスを供給し排気して化学的蒸着法により基板上に金属膜を形成する工程と、処理容器内にアルミニウム原子を含む原料ガスと窒素原子を含むガスとを供給し排気して化学的蒸着法により金属膜上に窒化アルミニウム膜を形成する工程と、金属膜および窒化アルミニウム膜形成後の基板を処理容器内から搬出する工程と、を有し、金属膜を形成する工程と窒化アルミニウム膜を形成する工程は、処理容器内を非酸素雰囲気に保った状態で連続的に行われる。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を拡大し、駆動電流の増大を図ることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2に埋め込まれた埋込み絶縁膜3により絶縁分離された活性領域5と、活性領域5上に形成されたゲート絶縁膜6を介して当該活性領域5を跨ぐように形成されたゲート電極7と、ゲート電極7を挟んだ両側の活性領域5にイオン注入することによって形成されたソース領域8及びドレイン領域9とを備え、活性領域5に溝部10が設けられて、この溝部10の内側にゲート絶縁膜6を介してゲート電極7の一部が埋め込まれてなるトレンチ型のチャネル構造を有し、活性領域5の両側面に凹部11が対向して設けられて、これら凹部11の間に幅狭部12が形成されることによって、少なくとも溝部10の底面と幅狭部12との間に当該幅狭部12よりも幅広となるチャネル領域13が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】酸化処理前における基板表面の初期酸化を抑えることができるとともに、自然酸化膜を除去できるようにする。

【解決手段】基板を処理室内に搬入する工程と、処理室内に酸素含有ガスと水素含有ガスとを供給して前記基板を処理する工程と、処理後の基板を処理室内より搬出する工程とを有し、処理工程では、処理室内の圧力を大気圧未満の圧力として処理室内に水素含有ガスを先行して導入し、続いて水素含有ガスの導入を維持した状態で酸素含有ガスを導入し、その後、水素含有ガスの導入を維持した状態で酸素含有ガスの導入を停止する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

電界効果トランジスタ

【課題】オン動作時における耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、キャリア走行層上に形成され、キャリア走行層とは反対の導電型を有し、キャリア走行層に到る深さまで形成されたリセス部によって分離したキャリア供給層と、分離した各キャリア供給層上にリセス部を挟んで形成されたソース電極およびドレイン電極と、分離した各キャリア供給層上にわたってリセス部内におけるキャリア走行層の表面を覆うように形成されたゲート絶縁膜と、リセス部においてゲート絶縁膜上に形成されたゲート電極と、を備え、ソース電極側のキャリア供給層は、該ソース電極直下に位置するソースコンタクト領域と、ゲート電極の下方に位置し、ソースコンタクト領域よりもキャリア濃度が低いソース電界緩和領域とを有する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルメタルゲート構造を有する半導体装置において、ゲート電極除去する工程において、ゲート絶縁膜に与える損傷を抑える。

【解決手段】 第1のトランジスタと第2のトランジスタとを備える半導体装置において、第1のトランジスタは、第1の仕事関数を有する第1の材料からなる第1のゲート電極と、第1のゲート絶縁膜とを含む。また、第2のトランジスタは、第2の仕事関数を有する第2の材料からなる第2のゲート電極と、第2のゲート絶縁膜とを含む。ここで、第1のゲート絶縁膜は、高誘電率膜と、第1の高誘電率膜上に形成された第1の絶縁膜とを含むものとする。第2のゲート絶縁膜においては、高誘電率膜上部に形成した第1の絶縁膜を、第1のゲート電極を除去した後に除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

41 - 60 / 221

[ Back to top ]