Fターム[5H740AA04]の内容

Fターム[5H740AA04]に分類される特許

121 - 140 / 444

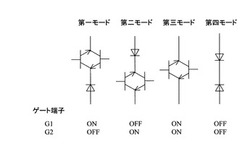

双方向スイッチのゲート駆動方法およびそれを用いた電力変換装置

【課題】インバータ等に適用される半導体デバイスとして双方向デバイスを適用した場合に、意図しない過渡期における各部の過電流や過電圧の発生を未然に防止して、低損失なゲート駆動方法を提供することを目的としている。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、双方向にオフ状態から双方向にオン状態へと移行する際に、直接移行しないように制御する制御手段を備え、双方向にダイオードを介在させない動作モードで主として動作し、過渡期においてはダイオードを介する動作が可能なため、低損失かつ各部の過電圧、過電流を防止できる効果が得られる。

(もっと読む)

半導体電力変換装置

【課題】トランジスタ素子のエミッタ−コレクタ間のサージ電圧を確実に収束させることができる半導体電力変換装置を提供する。

【解決手段】半導体電力変換装置1は、IGBT4と、このIGBT4に逆並列に接続されたダイオード5と、IGBT4のゲートに並列に接続されたゲート抵抗8a〜8dと、IGBT4がONからOFFに切り換わる時のIGBT4のエミッタ−コレクタ間のサージ電圧を検出するコレクタ電圧検知回路12と、このコレクタ電圧検知回路12の検出値と基準電圧V1との大小を比較するコンパレータ13と、このコンパレータ13の出力データに応じてカウンタ値をカウントアップまたはカウントダウンさせるカウンタ14と、このカウンタ14のカウンタ値に応じてIGBT4をOFF駆動するためのゲート抵抗8a〜8dを選択する抵抗選択回路15とを備えている。

(もっと読む)

貫通電流防止回路および車両用モータ駆動回路

【課題】半導体スイッチング素子の実動作に応じて貫通電流を防止することで動作信頼性を向上する。

【解決手段】下アーム側のIGBT(BTU2)に流れる通電電流を測定するときに、トランジスタQ2がIGBT(BTU2)の通電電流を直列抵抗R1およびR2の印加電圧によってセンシングする。そしてトランジスタQ3がトランジスタQ2の出力信号をレベルシフトする。そして、トランジスタQ4がトランジスタQ3のエミッタ電圧に応じてIGBT(BTU1)を強制的にオフ制御する。

(もっと読む)

アクティブスナバを有する電源スイッチ

【解決手段】本発明はアクティブスナバを有する電源スイッチに関する。第1の実施形態において、電子回路は,第1のパワー半導体装置と第1のパワー半導体装置に接続された第2のパワー半導体装置とで構成されている。第2のパワー半導体装置は、第1のパワー半導体装置のリンギングを阻止するように形成されている。 (もっと読む)

単相あるいは三相インバータおよびそれを用いた空気調和機

【課題】誘導負荷に使用される単相あるいは三相インバータにおいて、単方向スイッチと双方向性スイッチを組合せ、インバータ損失の低減と簡単なゲート駆動回路構成による低コスト化を目的とする。

【解決手段】上アームを単方向スイッチ17、下アームに双方向スイッチ1を接続したハーフブリッジ回路18を並列に接続してインバータを構成し、唯一のゲート駆動電源22にて各単方向スイッチ17、および双方向スイッチ1の駆動電源を共用することで簡単な回路構成にて駆動することができるインバータ装置を提供することを目的とする。

(もっと読む)

電源装置

【課題】安定した直流電流を出力できる電源装置を提供すること。

【解決手段】電源装置1は、トライアックTを有する位相制御回路110と、AC/DCコンバータ20と、を備える。AC/DCコンバータ20は、ノイズフィルタ121と、DC/DCコンバータ123と、トライアックTの他端に接続された整流回路122と、整流回路122とノイズフィルタ121との間に設けられたダイオードDと、整流回路122の後段に設けられた定電流回路24と、を備える。

(もっと読む)

パワースイッチング素子直列電圧制限回路

【課題】 パワースイッチング素子直列電圧制限回路を提供する。

【解決手段】 パワースイッチング素子直列電圧制限回路は、複数のパワースイッチング素子(Q1〜Qn)などからなるパワースイッチング素子直列分岐回路を含み、当該パワースイッチング素子は制御端と、高端(SD)と低端(WD)とを含み、パワースイッチング素子は分岐回路に直列にされるが、当該複数のパワースイッチング素子(Q1〜Qn)直列方式は1つのパワースイッチング素子における高端(SD)と別の1つのパワースイッチング素子における低端(WD)とを順に従って直列する。また、複数のエネルギー一時記憶回路(K1〜Kn)を含み、各パワースイッチング素子の両端が1つのエネルギー一時記憶回路を対応並列するが、各パワースイッチング素子の開/閉が非同期短時間過電流の負荷エネルギーを記憶するためである。また、前記パワースイッチング素子直列分岐回路に電圧制限を行う集中電圧制限回路Hを含む。

(もっと読む)

過電圧保護回路、及び過電圧保護方法

【課題】電圧供給が不必要に遮断されてしまうことのない、過電圧保護回路および過電圧保護法方を提供する。

【解決手段】第1入力ラインに設けられ、所定値以上の電流が流れると切断される過電流遮断回路と、第1入力ラインと第2入力ラインとの間に介装されるサイリスタと、サイリスタと第1入力ラインとの間に介装され、サイリスタと第1入力ラインとを導通させるか否かを切り替えるスイッチ回路と、第1入力ラインと第2入力ラインとの間の電圧差が予め設定された制限電圧以上になった場合に第1入力ラインをサイリスタのゲートと導通させる過電圧検出回路と、スイッチ回路の動作を制御する制御回路とを具備する。制御手段は、サイリスタのゲートにゲートトリガ以上の電圧が印加された期間が予め設定された制限期間を超えた場合に、サイリスタと第1入力ラインとを導通させるように、スイッチ回路の動作を制御する。

(もっと読む)

ゲートドライバのためのオプトカプラ回路

オプトカプラ回路10は、フォトLED20と並列接続するスイッチ22を含み、フォトLED20はアノード及びカソードを有する。アノードは減結合コンデンサ28を介して電源に接続される。オプトカプラ回路は、スイッチが開放位置にあるときフォトLEDをオンにするよう構成される。スイッチが閉じているときは、スイッチ22は電流の流れの向きを、直列抵抗器32を経由して接地へ向けるようにし、電流の流れを分流してフォトLEDから離すことでフォトLEDをオフにする。第2のコンデンサ38は、フォトLEDのカソードへ接続される。第2のコンデンサは、第2のスイッチ40及び接地へ接続された電流制限抵抗器42と直列に配線される。第1のスイッチ22及び第2のスイッチ40は、カソードが接続されたコンデンサ38の放電を回避するために相補状態で動作する。開示されるオプトカプラ回路10は、より高レベルのコモンモード電圧過渡現象で機能する性能を提供する。  (もっと読む)

(もっと読む)

電力変換装置のスナバ回路

【課題】並列接続された各半導体素子をスイッチング素子とする電力変換装置において、配線の長短により電流アンバランスが生じる場合でも、各半導体素子のターンオフ損失のアンバランスを抑制し損失を低減できるようにする。

【解決手段】2つの半導体素子11,12を並列接続した上アームのみについて、配線インダクタンス5を等価回路で表わした図示のような電力変換装置では、配線の長短によりインダクタンスが異なることで電流アンバランスが生じるので、配線長の長くなる方のスナバコンデンサ(同図ではCs2)の容量よりも、短くなる方のスナバコンデンサの容量を大きくすることにより、掲記課題の解決を図る。

(もっと読む)

コンバータの制御回路

【課題】高効率且つ低ノイズを実現するコンバータの制御回路を提供する。

【解決手段】実施形態によれば、コンバータの制御回路は、ハイサイドスイッチング素子のゲートに接続されハイサイドスイッチング素子のゲートを駆動するドライブ回路と、ドライブ回路と並列にハイサイドスイッチング素子のゲートに接続されたドライブスイッチと、ドライブスイッチに制御信号を供給してドライブスイッチをオンオフするドライブスイッチ制御回路とを備えている。ハイサイドスイッチング素子がドライブ回路によって駆動されている期間中、ハイサイドスイッチング素子のゲート電圧が所定の閾値に達すると、ドライブスイッチ制御回路はドライブスイッチに制御信号を供給してドライブスイッチをオンからオフに切り替える。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、入力信号を反転した信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

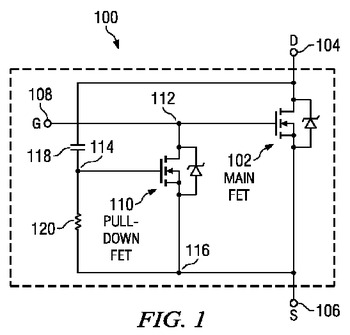

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】電圧駆動型半導体素子のスイッチング時に配線インダクタンスにより発生する素子間のサージ電圧を低減するためにゲート駆動回路のゲート抵抗を大きくすると、スイッチングの動作遅れ時間が長くなる。

【解決手段】電圧駆動型半導体素子のターンオフ時において、オフ信号によりゲート電荷を放電させる時にはオフ信号印加の初めに第1の抵抗体とコンデンサにより早く放電させることにより、スイッチング動作時間遅れの増加を防止し、その後第2の抵抗体に切換ることによりゲート電流を減少させることによって、素子間のサージ電圧を低減する。また、電圧駆動型半導体素子のターンオン時には、ダイオードが導通状態となることにより、該第1の抵抗体と該第2の抵抗体が並列構成となるので、前記第1の抵抗体の抵抗値により、早くゲート電荷を充電することができる。

(もっと読む)

スイッチング素子の駆動装置

【課題】第1スイッチング素子22および第1抵抗体24を介してパワースイッチング素子Swのゲートと電源20とを接続して且つ、第2スイッチング素子28および第2抵抗体26を介してゲートとエミッタとを接続する駆動装置において、ゲート電圧の設定ができないこと。

【解決手段】操作信号gがパワースイッチング素子Swをオン操作する指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態を実現する。これにより、ゲート印加電圧は、第1抵抗体24および第2抵抗体26によって電源20が分圧された電圧Vcとなる。その後、ミラー期間が終了することで、第2スイッチング素子28をオフ状態に切り替え、ゲート印加電圧を電源20の電圧Vcにする。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】低コストで実現でき、小型化、低消費電力化及び高周波化に資するとともに、フリップフロップ回路の誤動作を防止するレベルシフト回路及びレベルシフト回路を用いたスイッチング電源装置を提供する。

【解決手段】それぞれ一端がレベルシフト電源に接続された抵抗R1、R2と、抵抗R1の他端にドレインが接続されたトランジスタMN3と、抵抗R2の他端にドレインが接続されたトランジスタMN4と、入力信号に基づいてトランジスタMN3,MN4のオン/オフを制御するパルス発生回路10と、トランジスタMN3がオンである場合にセット信号、トランジスタMN4がオンである場合にリセット信号を生成する制御部と、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12とを備える。

(もっと読む)

スイッチの制御を簡略化するための方法と装置

【課題】スイッチの制御を簡略化するための技法を提供する。

【解決手段】実施の一形態では、スイッチの両端の電圧の関数としてスイッチを制御する方法を提供する。実施の一形態では、スイッチの両端の電圧の傾斜の関数としてスイッチを制御する方法を提供する。実施の一形態では、スイッチがオフになっている間のスイッチの両端の電圧に応答して実質的に固定されたオン時間中スイッチをオンに切り替えている。実施の一形態では、スイッチがオフになっている間のスイッチの両端の電圧の傾斜に応答して実質的に固定されたオン時間中スイッチをオンに切り替えている。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

半導体駆動回路、及びそれを用いた半導体装置

【課題】ノーマリオフの接合型FETは閾値が低いため、ノーマリオフの接合型FETを用いた半導体駆動回路では高精度な電圧制御,高速な入力容量の充電,誤動作等の課題を有していた。

【解決手段】ツェナーダイオードによる高精度なゲート電圧生成方式やスピードアップコンデンサによるターンオン損失の低減,ゲート・ソース間のコンデンサの接続やソース端子の最適実装方式による誤動作の防止回路を適用することで、ノーマリオフの接合型FETに最良な半導体駆動回路を提案する。

(もっと読む)

出力回路

【課題】貫通電流を防止する。

【解決手段】ローサイドオフ検出回路10は、ローサイドトランジスタM2のゲート信号SGLを所定の第1レベルTHLと比較することによって、ローサイドトランジスタM2がオフしたことを示すローサイドオフ検出信号S1を生成する。ローサイド検出トランジスタMSLは、ローサイドトランジスタM2と同型であり、そのソースが接地端子108に接続され、そのゲートにローサイドトランジスタM2のゲート信号SGLを受ける。第1抵抗R11は、ローサイド検出トランジスタMSLのドレインと電源端子106の間に設けられる。第1バイパス回路12は、第1抵抗R11と並列に設けられ、制御信号SINがローサイドトランジスタM2のオフを指示するレベルをとるときに導通し、オンを指示するレベルをとるとき遮断する。ローサイド検出トランジスタMSLのドレインの信号が、ローサイドオフ検出信号S1として出力される。

(もっと読む)

121 - 140 / 444

[ Back to top ]