Fターム[5J055EX02]の内容

Fターム[5J055EX02]の下位に属するFターム

フリップフロップ (36)

Fターム[5J055EX02]に分類される特許

101 - 120 / 1,031

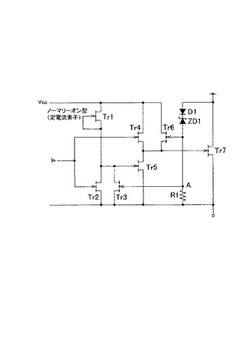

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

リセット回路

【課題】マイクロコンピュータとCPUを安全かつ確実にリセットして正常起動させる。

【解決手段】第1制御回路41は第2電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC20は第1電圧をレギュレートして生成した第2電圧を第1制御回路41に供給し、第2制御回路42は第3電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC30は、第3電圧をレギュレートして生成した第4電圧を第2制御回路42に供給する機器において、リセット回路100は、第1電圧が第5電圧を超えて150msが経過するまでリセット信号の出力を継続させ、第1電圧が第5電圧を超えてから150msが経過するとリセット信号の出力を停止する。(第1電圧≧第2電圧、第3電圧≧第4電圧、第1電圧>第3電圧、第5電圧>第2電圧)

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

高圧パルス発生装置

【課題】小型且つ低価格な高圧パルス発生装置を提供する。

【解決手段】高圧パルス発生装置は、パルス信号を発生するパルス発生部1と、高圧側電圧VDDを生成する高圧側電源2と、低圧側電圧VSSを生成する低圧側電源3と、前記パルス信号に応じて、入力された前記高圧側電圧VDDと前記低圧側電圧VSSとを何れか一方ずつ交互に出力端子O1から出力するスイッチング部4と、前記パルス信号の周波数と、前記高圧側電圧VDDと、前記低圧側電圧VSSとを制御する制御部5と、を備える。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

故障または異常検出機能を有するパルス増幅装置およびパルス増幅器故障検出方法

【課題】小型化が可能な故障または異常検出機能を有するパルス増幅装置を提供すること。

【解決手段】本実施形態に係る故障または異常検出機能を有するパルス増幅装置は、入力されるパルスを増幅して出力するパルス増幅器11と、パルス増幅器11の入力端子に接続され、パルス増幅器11に入力されるパルスに同期したパルス増幅器11を動作させる制御信号を形成して、この制御信号を入力端子に入力するパルス増幅器制御回路12と、パルス増幅器制御回路12に接続され、制御信号を連続波に変換する平均化回路17と、平均化回路17に接続され、平均化回路17から出力された連続波の電圧Vgaveとしきい値電圧Vsとを比較する比較回路18と、比較回路18に接続され、比較回路18から出力される差分電圧(Vgave−Vs)に基づいて、パルス増幅器11の故障、あるいはパルス増幅器制御回路12の異常を検出する警報装置23と、を具備する。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障等してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用抵抗121bの端子間電圧に基づいてオン駆動用FET121aに流れる電流を検出する。そして、駆動信号がIGBT110dのオフを指示しているにもかかわらず、オン駆動用FET121aに電流が流れているとき、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。従って、オン駆動用スイッチング素子がオン故障等した場合であっても、スイッチング素子の熱破壊を防止することができる。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

外部アダプター

【課題】 消費電力の少ない回路によって2線式電子スイッチのON/OFF状態を的確に検出できる外部アダプターを提供する。

【解決手段】 外部アダプター11は、電子スイッチ1に接続される2つの入力端子12,13を備える。分圧抵抗器R1,R2は入力電圧を分圧し、分圧抵抗器R2の両端電圧に基づいて、フォトカプラー14が電子スイッチ1のON/OFF状態を検出する。インピーダンス調整回路19は、入力端子12,13間に介装された調整抵抗器R3、フォトカプラー14の出力に応答して調整抵抗器R3への通電/遮断を切り替えるトランジスタQ1およびフォトMOSリレー18を備え、アダプター11の入力インピーダンスを電子スイッチ1の接点導通状態で相対的に高く、接点非導通状態で相対的に低く調整する。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

スイッチ回路、半導体装置及び携帯無線機

【課題】負バイアス発生回路を用いずにマージン電圧を改善することができる手段をスイッチ回路に提供する。

【解決手段】N型MOSFETを用いて構成されるスイッチM1を、信号をアンテナに同通するスイッチに、P型MOSFETを用いて構成されるスイッチM2を、信号を接地するシャント用にそれぞれ用いる。各スイッチを構成するMOSFETのゲート端子に共通の制御信号を入力する。この制御信号の反転信号をスイッチM2の接地端に接続することで、各MOSFETのゲート端子の電位を接地電圧に設定できる。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

101 - 120 / 1,031

[ Back to top ]