Fターム[5J106GG01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 発振回路、VCO (652)

Fターム[5J106GG01]の下位に属するFターム

原子発振器 (61)

基準・局部・予備発振回路 (39)

Fターム[5J106GG01]に分類される特許

141 - 160 / 552

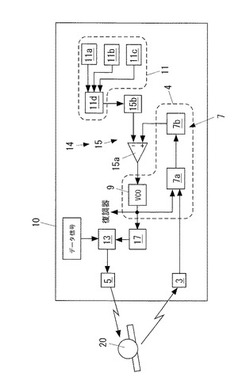

通信装置

【課題】飛翔体に搭載され衛星と通信を行う通信装置において、飛翔体からの送信信号の周波数がドップラー効果により大きく変動した場合であっても、送信信号を所定の規定周波数で衛星が受信できるようにする。

【解決手段】飛翔体に搭載され衛星20と通信を行う通信装置10であって、衛星20に対し送信信号を送信する送信部5と、衛星20に対する飛翔体の相対位置、姿勢、速度に基づいて、ドップラー効果による送信信号の周波数変動量を求める周波数変動量取得部14と、衛星20から見た送信信号の周波数が規定周波数となるように、周波数変動量に基づいて、送信信号の周波数を調整する送信信号調整部13と、を備える。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

PLL装置及び不要周波数回避方法

【課題】PLL装置において、不要周波数の影響を、無線性能に影響を与えることなく回避できるようにする。

【解決手段】電圧制御発振器3、4と、基準信号に基づく第1信号及び電圧制御発振器の出力信号に基づく第2信号の両位相を比較し、位相差を示す位相差信号を出力する位相比較器1と、位相差信号に基づき、両位相を同期させる制御電圧を電圧制御発振器に印加するループフィルタ2とを備え、所定の目的周波数を得るPLL装置において、目的周波数を中心とする所定の周波数範囲内に不要周波数が存在する場合に、不要周波数を該周波数範囲外のものとするために基準信号の周波数を変更する基準周波数変更手段5と、基準信号の周波数の変更にも拘わらず目的周波数の出力が維持されるように、第1信号又は第2信号を生成する際の分周比を変更する分周比変更手段5とを設ける。

(もっと読む)

周波数掃引方法及び回路

【課題】階段状波形による繰返し周波数信号が生成されることなく、高速掃引が可能となり、また温度等の環境条件に左右されることなく、周波数制御を安定して行う。

【解決手段】VCO1からの出力をプログラマブルカウンタ14、PFD16、安定化フィルタ17及び傾き制御用フィルタ18を介して帰還させるループを形成し、プログラマブルカウンタ14からの現在の周波数ポイントの制御信号に基づく周波数引込み時間内に、次の周波数ポイントの制御信号をPFD16に出力し、位相同期状態を経ることなく、連続した周波数の掃引を実行する。上記傾き制御用フィルタ18では、掃引における周波数変化の傾きを制御する。

(もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

周波数シンセサイザ

【課題】バラツキ耐性を強くし、温度変動のときに、VCOの周波数変動を補償する周波数シンセサイザの提供。

【解決手段】VCO5と、VCOの発振出力を可変分周回路4で分周した信号22と基準発振回路1の基準信号21を位相比較する位相比較器2と、位相比較結果に基づきVCOへの制御電圧23を生成するループフィルタ3とがPLLを構成し、VCOは、複数の重み付けされた容量素子56〜58と制御信号に基づきオン・オフされる複数のスイッチを備えた容量バンクと、バラクタ54を備える。温度補償ブロック7は、バラクタの補正電位発生回路73と、容量バンクの寄生容量の補正電位発生回路71と、該補正電位発生回路の出力電位を制御信号に基づき重み付け処理するゲイン可変アンプと、バラクタの補正電位発生回路の出力電圧とゲイン可変アンプの出力電圧を加算する加算回路79とを備え、加算回路の出力25によりVCOのバラクタが制御される。

(もっと読む)

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

141 - 160 / 552

[ Back to top ]