Fターム[5J106GG01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 発振回路、VCO (652)

Fターム[5J106GG01]の下位に属するFターム

原子発振器 (61)

基準・局部・予備発振回路 (39)

Fターム[5J106GG01]に分類される特許

101 - 120 / 552

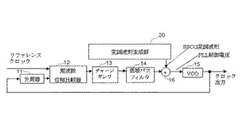

クロック生成回路と半導体装置及びクロック生成方法

【課題】スペクトルの抑圧効果の高い変調波形を得ることができ、Hershey−kissによる変調方式と比べ、回路規模を小さくするクロック生成回路の提供。

【解決手段】変調波形生成部20は、SSCG変調波形として、tan波形またはtan+三角波を生成し、PLLループの低域パスフィルタ14の出力に、該SSCG変調波形を合成した信号を発振器(VCO)15に与える。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

半導体集積回路及びそれを用いた電子機器

【課題】低速ディジタル回路において発生するノイズがアナログ回路に与える影響を小さくし、回路ブロック毎のレイアウト変更を容易にする。

【解決手段】半導体集積回路は、(a)第1及び第2のVCOと、第1及び第2のVCOによって生成される信号を分周する第1及び第2の分周回路と、2つの分周信号の内の一方を選択する選択回路と、選択された分周信号に基づいて制御電圧を生成する制御電圧生成回路とを含むアナログ回路ブロックと、(b)変復調回路を含む第1のディジタル回路ブロックと、(c)制御回路を含む第2のディジタル回路ブロックとを備え、アナログ回路ブロックが、基板の第1及び第2の辺に沿って配置され、第2のディジタル回路ブロックが、基板の第3及び第4の辺に沿って配置され、第1のディジタル回路ブロックが、アナログ回路ブロックと第2のディジタル回路ブロックとの間に配置されている。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

通信システム

【課題】製造ばらつき・温度変動に依存することなく、受信状態又は送信状態を良好に保つ事が出来る通信システムを提供すること。

【解決手段】電圧制御発振部(106)の発振周波数を制御するように、位相同期回路(100)からの周波数制御信号(c1)を用いて、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つの同調周波数を制御することで、受信周波数の同調を行い、Q値制御回路(110)からのQ値制御信号(b1)を用いて第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値制御用可変抵抗の抵抗値を可変することにより、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値を制御して、受信帯域の最適化を行う。

(もっと読む)

位相ロックループ回路およびそれを用いた電子機器

【課題】gm−C型VCOを用いたPLL回路において、VCOをgmセルのトランスコンダクタンス(α・gm)と、キャパシタの容量値Cの比で定まる発振周波数で確実に発振させる。

【解決手段】gm−C型VCO10は、入力された制御電圧Vtuneに応じた周波数で発振する。分周器4は、gm−C型VCO10から出力される発振信号Voscを分周する。位相比較信号生成部5は、分周器4により分周された発振信号Vosc’と、基準クロック信号CLKの位相差に応じた位相差信号Vpdを発生する。ループフィルタ6は、位相差信号Vpdをフィルタリングし、制御電圧Vtuneを生成する。スタートアップ回路8は、制御電圧Vtuneに応じた検出信号Vsのレベルにもとづいたタイミングにおいて、gm−C型VCO10にシードパルスS3を注入する。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

基準周波数発生装置

【課題】長時間にわたって基準周波数周波数の周波数安定度を維持可能で、かつ安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置1は、ルビジウム発振器11と、ルビジウム発振器11より周波数安定度が低い水晶発振器21と、判定部42と、切替スイッチ51a〜51fと、を備える。判定部42は、ルビジウム発振器11が正常な出力信号を出力している正常状態か、正常な出力信号を出力していない故障状態か、を判定する。切替スイッチ51c,51dは、ルビジウム発振器11が正常状態であると判定部42が判定しているときは、第1PLL回路を構成するように設定を行い、ルビジウム発振器11が故障状態であると判定部42が判定しているときは、第2PLL回路を構成するように設定を行う。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

位相同期発振装置

【課題】 小さいばらつきで電圧制御回路から供給される温度補償された電圧によって制御される電圧制御発振器を介して接続された増幅器の出力電力を、精度良く増減させ出力端子から出力する位相同期発振装置を得る。

【解決手段】 発振周波数を制御する周波数制御電圧入力端子と発振電力を制御する電圧入力端子とを有する電圧制御発振器と、この電圧制御発振器から出力される高周波信号を増幅して出力する温度特性を有する増幅器と、温度センサを有し、この温度センサの出力信号で基準電圧から変化する電圧を前記電圧制御発振器の電圧入力端子に入力し、前記電圧制御発振器を介して前記増幅器の電力非飽和領域の電力を増減する電圧制御回路とを備えている。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

【課題】フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)の提供。

【解決手段】二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

周波数−電流フィードバックを有する温度安定形発振回路

フェーズロックループや低周波温度安定形発振器を必要としない信号生成回路(600)および方法が開示される。この方法は、振動出力信号の周波数を制御するフィードバック信号(608)に応じて振動出力信号(CLK1〜CLKN)を生成することと、振動出力信号の周波数に対応する大きさを有する電流出力信号を生成することと、フィードバック信号を生成するために電流出力信号を基準信号(654)と比較することとを含んでよい。信号生成回路(600)は、フィードバック信号(608)に反応する発振回路(602)と、振動出力信号の周波数に対応する周波数依存性電流信号を生成する周波数−電流変換回路(620)とを含んでよい。発振回路へ向けてフィードバック信号(608)を生成するため、フィードバック変換回路(612)は出力信号を基準信号(654)と比較する。  (もっと読む)

(もっと読む)

101 - 120 / 552

[ Back to top ]