Fターム[5J106GG01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 発振回路、VCO (652)

Fターム[5J106GG01]の下位に属するFターム

原子発振器 (61)

基準・局部・予備発振回路 (39)

Fターム[5J106GG01]に分類される特許

121 - 140 / 552

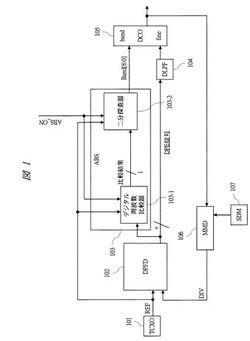

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

クロック信号生成装置、電子装置、及び、PLL(PhaseLockedLoop)制御装置

【課題】所定のクロック信号の周波数を短時間で変更するとともに、クロック信号の周波数の変更時にクロック信号の供給先の動作が不安定になることを防止又は軽減するクロック信号生成装置等を提供する。

【解決手段】クロック信号生成装置等は、目標周波数が変更されると、第1制御部の代わりに、予め設定されている期間内に予め設定されている間隔かつ予め設定されている変更値で、クロック信号生成部に印加する電圧を順次変更し、クロック信号生成部が新たに生成するクロック信号の周波数を目標周波数に近づかせる第2制御部を備える。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

原子発振器、及び光源を制御する方法

【課題】透過光強度が最小となる点に直流バイアス電流を追い込むことが可能な原子発振

器を提供する。

【解決手段】アルカリ金属原子に電磁誘起透過現象を発生させるための共鳴光対を生成す

る半導体レーザー1と、アルカリ金属原子を封入したcell2と、cell2を透過し

た共鳴光対を検出するPD3と、PD3の出力信号をデジタル信号に変換するA/Dコン

バーター4と、A/Dコンバーター4により変換されたデジタル信号を記憶するメモリ6

と、メモリ6へデジタル信号を書き込み、メモリ6に記憶されたデジタル信号を読み出す

メモリ制御部5と、メモリ6に既に記憶されているデジタルデータとA/Dコンバーター

4により変換されたデジタル信号とを比較する比較部7と、比較結果に基づき半導体レー

ザー1に与える直流バイアス電流を制御する電流源制御部8と、半導体レーザー1に直流

バイアス電流を供給する電流源9と、を備えて構成されている。

(もっと読む)

発振回路

【課題】 起動直後から安定した振動波形を有する出力信号を得ることができる発振回路を提供する。

【解決手段】 発振回路1Aは、入力電圧に基づいて振動波形を有する振動出力電圧を出力する主発振回路2Aと、主発振回路2Aの振動出力電圧に応じた出力信号と予め定められた周波数を有するクロック同期信号SYNCとが入力され、出力信号及びクロック同期信号SYNCの位相差に応じた電圧を出力する位相比較器3と、位相比較器3の出力電圧を平滑化する第1ローパスフィルタ4と、第1ローパスフィルタ4の出力電圧が基準電圧Vref1以上の場合、第1ローパスフィルタ4の出力電圧を主発振回路2Aに入力し、第1ローパスフィルタ4の出力電圧が基準電圧Vref1より低い場合、基準電圧Vref1を主発振回路2Aに入力する切替回路5Aとを備えている。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有することが可能なPLL回路等を提供すること。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

周波数測定回路及びそれを有するPLLシンセサイザ

【課題】

被測定クロックの周期または周波数を高精度に計測する周波数計測回路を提供する。

【解決手段】

周波数測定回路は,被測定クロックの被測定エッジをカウントするカウンタと,基準クロックの基準エッジに応答して,前記カウンタのカウント値を記憶するカウンタラッチ回路と,直列に接続された複数の基本遅延回路を有し,前記被測定クロックを初段の前記基本遅延回路に入力して伝搬させる遅延回路と,前記基準エッジに応答して,前記遅延回路の複数の基本遅延回路の出力をそれぞれラッチする複数の遅延ラッチ回路と,前記遅延ラッチ回路がラッチした前記複数の基本遅延回路の出力に基づいて,前記被測定クロックの前記被測定エッジの前記遅延回路内での位置を検出するエッジ検出回路と,2つの基準エッジ間の前記カウント値と,前記2つの基準エッジでの前記第1のエッジ検出回路が検出する前記被測定エッジの位置情報とから,前記被測定クロックの周期または周波数を演算する演算器とを有する。

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

デジタル位相同期回路

【課題】ホールドオーバ期間中の温度特性と経年変化に対する影響を抑え、周波数の高安定性を維持するホールドオーバ機能を有するデジタル位相同期回路を得る。

【解決手段】電圧制御型クロック発振手段の周辺の温度を測定する温度測定手段と、同期対象と同期している間、デジタルフィルタ手段からの出力で電圧制御型クロック発振手段を制御するとともにデジタルフィルタ手段からの出力と電圧制御型クロック発振手段の周辺の温度、経過時問の履歴から経過時間と電圧制御型クロック発振手段の周辺の温度と項に持つ2元多項式を求め、同期対象と同期していない間、同期対象に同期しなくなってからの経過時間および電圧制御型クロック発振手段の周辺の温度から2元多項式で電圧制御型クロック発振手段を制御する制御信号を推定するとともに推定した制御信号で電圧制御型クロック発振手段を制御するホールドオーバ手段と、を有する。

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

PLL回路

【課題】 エージング特性を自動補正し、外部基準信号の未接続又はアンロック時に出力周波数変動を小さくできるPLL回路を提供する。

【解決手段】 基準信号が適正範囲内でロック状態の場合に、初期調整時に、チャージポンプ出力電圧(A)の初期電圧を温度情報Tと共に読み取り、自走周波数設定用電圧(B)が電圧(A)となるようのDAコンバータ又はPWM出力回路9の設定値を調整し、温度特性初期テーブルを生成し、運用中に、温度情報Tにおける電圧(A)の最新電圧に対応する設定値を、温度特性初期テーブルを参照して特定し、初期電圧と最新電圧の設定値の差分で当該テーブルをオフセット補正して自走用温度補正テーブルを生成し、アンロック状態等になると特定された設定値による自走周波数設定用電圧(B)で自走するPLL回路である。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

121 - 140 / 552

[ Back to top ]