国際特許分類[H02M1/00]の内容

電気 (1,674,590) | 電力の発電,変換,配電 (135,566) | 交流−交流,交流−直流または直流−直流変換装置,および主要な,または類似の電力供給システムと共に使用するための装置:直流または交流入力−サージ出力変換;そのための制御または調整 (22,926) | 変換装置の細部[1,2007.01] (2,099)

国際特許分類[H02M1/00]の下位に属する分類

静止型変換器に用いられる放電管の格子制御またはイグナイタ制御電力の発生に用いられる回路

ガス放電管または等価の半導体装置,例.サイラトロン,サイリスタ,を非導通にするために特に適合した回路 (6)

静止型変換器に用いられる半導体装置の制御電圧の発生に用いられる回路 (988)

異なった種類の供給電力,例.交流または直流,から負荷を運転させるための変換装置に用いられる装置 (23)

交流入力または出力から高調波を減少させるための装置 (169)

直流入力または出力からリップルを減少させるための装置 (69)

回路の開閉時に立ち上がり電流を供給するための装置,例.可飽和リアクトルをもつもの (1)

非静止型変換器の接点機構

自動切断によるもの以外の、変換器を保護するための手段 (29)

変換器を起動または停止するための手段 (4)

スイッチング手段が同時導通することを防止するための手段 (7)

磁気的飽和することを防止する手段

変換器の力率を補正または調節するための回路または装置 (6)

変換器の電磁妨害を補償するための回路または装置 (53)

国際特許分類[H02M1/00]に分類される特許

11 - 20 / 744

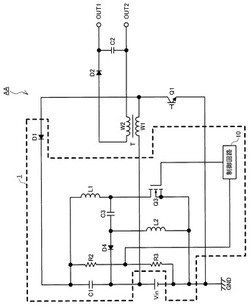

耐圧保護回路

【課題】スイッチ素子の耐圧保護回路について、損失を抑制しつつ、設計容易性を向上させること。

【解決手段】耐圧保護回路1は、キャパシタC1、C3と、インダクタL1、L2と、スイッチ素子Q3と、制御回路10と、を備える。キャパシタC1の他方の電極には、直流電源Vinの正極が接続され、キャパシタC1はサージ電圧を吸収する。キャパシタC3の一方の電極には、ダイオードD4を介して直流電源Vinの正極が接続される。キャパシタC1の一方の電極には、インダクタL1を介してキャパシタC3の他方の電極が接続されるとともに、スイッチ素子Q3のドレインが接続される。スイッチ素子Q3のソースには、直流電源Vinの負極が接続され、スイッチ素子Q3のゲートには、制御回路10が接続される。制御回路10は、キャパシタC1の端子間電圧が閾値電圧以上であれば、スイッチ素子Q3をスイッチングさせる。

(もっと読む)

半導体装置における負荷電流のゼロ交差の検出

【課題】 半導体装置における負荷電流のゼロ交差検出を提供する。

【解決手段】 ゲート電極と、エミッタとコレクタ電極との間の負荷電流経路と、を有する逆導通トランジスタを含む回路装置が開示される。トランジスタは、負荷電流経路を介し順方向と逆方向に負荷電流を導通できるようにするとともにゲート電極においてそれぞれの信号により活性化または非活性化されるように構成される。回路装置はさらにゲート制御手段と監視手段を含む。ゲート制御手段はゲート電極に接続されるとともに、トランジスタが逆導通状態である場合にゲート電極を介しトランジスタを非活性化するまたはトランジスタの活性化を防止するように構成される。監視手段は、トランジスタが非活性化されるまたは非活性化がゲート制御手段により防止されている間に負荷電流がゼロを交差するときに発生する逆導通トランジスタのコレクタ−エミッタ電圧の突然の上昇を検出するように構成される。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

インバータ装置

【課題】複数のインバータの間における電圧の干渉による悪影響の抑制を、省スペースな装置において実現することができるインバータ装置を提供する。

【解決手段】インバータ装置は、PN母線に接続された第1インバータと、PN母線に接続された第2インバータと、PN母線における第1インバータと第2インバータの間に接続されたクランプ回路とを備える。クランプ回路は、ツェナーダイオードと、スイッチング素子とを備える。ツェナーダイオードは、PN母線におけるP母線にカソードが接続しN母線にアノードが接続する。スイッチング素子は、P母線とN母線との間に介在し、制御端子がツェナーダイオードのアノードと接続したものである。

(もっと読む)

過電圧保護回路

【課題】回路素子の耐圧を超える過電圧から回路を保護することができる過電圧保護回路を提供する。

【解決手段】コンパレータCP1は、検出電圧Vdetおよび電圧Vth1を比較し、その比較結果を表す比較信号Sc1を制御回路7に出力する。コンパレータCP2は、検出電圧Vdetおよび電圧Vth1より高い電圧Vth2を比較し、その比較結果を表す比較信号Sc2を制御回路7に出力する。制御回路7は、比較信号Sc1が反転する時点から比較信号Sc2が反転する時点までの経過時間が所定時間未満である場合、電圧VBの電圧変化率が所定値以上であり、直流電源線3、4間に回路素子の耐圧を超える過電圧が生じると判断する。制御回路7は、耐圧を超える過電圧が生じると判断した場合、短絡用トランジスタT2をオン駆動するなどの保護動作を実行する。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

負荷回路の制御装置

【課題】並列に接続したMOSFETの発熱を均一化することが可能な負荷回路の制御装置を提供する。

【解決手段】電源と負荷とを接続する負荷回路に、2個のMOSFET(Q1),(Q2)を並列に配置する。そして、各MOSFET(Q1),(Q2)が交互にオン、オフとなるように制御する。その結果、各MOSFET(Q1),(Q2)のいずれか一方にのみ電流が流れることになるので、電流センサ12,22で検出されるオフセット誤差は、いずれか一方のオフセット誤差のみとなり、高精度な電流検出が可能となる。従って、負荷に流れる電流が過電流となった際に回路を遮断する制御を行う際に、高精度な遮断制御が可能となる。

(もっと読む)

温度検知回路

【課題】電力変換器のヒートシンクに実装された複数のサーマルリードスイッチを使用した温度検知回路において、最小の構成にて、動作したサーマルリードスイッチを特定することが可能な温度検知回路を提供することである。

【解決手段】設定温度以上で開放するサーマルリードスイッチと並列に抵抗器を接続し、測定点分を直列に接続し、各抵抗器の抵抗値は異なる値とする。開放するサーマルリードスイッチにより、この直列体のインピーダンスが変化するため、抵抗値や分圧された電圧値を判別することで動作したサーマルリードスイッチを特定することができる。複数使用したサーマルリードスイッチの動作部位を簡略な回路構成にて判別することが可能である。

(もっと読む)

11 - 20 / 744

[ Back to top ]