Fターム[4K029DA08]の内容

Fターム[4K029DA08]に分類される特許

121 - 140 / 495

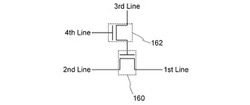

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

基板を熱処理する装置

本発明は、基板(20)を熱加工するための熱処理内側チャンバ(3)であって、壁(10)を備え、該壁(10)は、熱処理内側チャンバ(3)の内室(24)を包囲し、熱加工の間に基板(20)を支承するための支承装置(8)を備え、熱処理内側チャンバ(3)の内室(24)にエネルギを導入するためのエネルギ源(11)を備え、壁(10)の内側面の少なくとも一部は、エネルギ源(11)により導入される出力を反射するように形成されるものにおいて、壁(10)の内側面の少なくとも一部は、少なくとも赤外線高反射性の材料から成ることを特徴とする。さらに本発明は、基板(20)を熱加工するための熱処理内側チャンバ(3)であって、壁(10)を備え、該壁(10)は、熱処理内側チャンバ(3)の内室(24)を包囲し、熱加工の間に基板(20)を支承するための支承装置(8)を備え、熱処理内側チャンバ(3)の内室(24)にエネルギを導入するためのエネルギ源(11)を備えるものにおいて、壁(10)の少なくとも一部を冷却するための冷却装置(14)を設ける。  (もっと読む)

(もっと読む)

半導体エピタキシャルウェハの製造方法、半導体エピタキシャルウェハ及び半導体素子

【課題】MBE法又はMOCVD法により半導体基板上に半導体薄膜をエピタキシャル成長させる際に、半導体薄膜の特性を変えることなく、残留キャリアを低濃度に制御する技術を提供する。

【解決手段】半導体基板上に半導体薄膜をエピタキシャル成長させてなる半導体エピタキシャルウェハの製造方法において、半導体薄膜をエピタキシャル成長させる際、同時にアルミニウム(Al)をドープする。

(もっと読む)

スパッタリング装置および半導体発光素子の製造方法

【課題】基板を加熱する効率を向上させたスパッタリング装置およびそのスパッタリング装置による半導体発光素子の製造方法を提供する。

【解決手段】スパッタリング装置1は、内部が減圧状態に維持されてプラズマ放電20が形成されるチャンバ10と、チャンバ10内に設置され、ターゲット21を保持するカソード22と、基板110を保持し基板110の一表面がターゲット21の表面に対向するように基板110を保持する基板ホルダ60とを備えている。基板110はスパッタリング装置1の上方に基板110の表面を下方に向けて配置されている。ターゲット21はスパッタリング装置1の下方にターゲット21の表面を上方に向けて配置されている。スパッタリング装置1は、基板110を加熱するためのヒータ65を備えている。基板110は、ヒータ65から放射される電磁波を吸収することで温度が上昇する。

(もっと読む)

薄膜アクチュエータ、及びインクジェットヘッド

【課題】変位量が大きく、且つ信頼性の高い薄膜アクチュエータ、及びインクジェットヘッドを提供する。

【解決手段】基板101と、基板101の上に形成され、両端または周縁が基板101に固定された下電極膜103と、下電極膜103の上に形成され、駆動信号により膜面に沿った方向に伸縮する圧電体膜104と、圧電体膜104の上に形成された上電極膜105と、を有する薄膜アクチュエータ1であって、上電極膜105は、複数の電極膜から構成され、複数の電極膜のうち、圧電体膜104に接する電極膜は、初期応力としての引張応力を有し、圧電体膜104に接する電極膜の上層の電極膜は、引張応力よりも小さい初期応力を有している。

(もっと読む)

加熱装置及び基板処理装置

【課題】被加熱体の面内温度を均一にする。

【解決手段】被加熱体Wが搬出入される開口部6を有するチャンバ5と、前記チャンバ内に設けられ、被加熱体を加熱するためのヒータ10と、前記チャンバ内に設けられ、前記被加熱体を保持するための保持機構11と、前記ヒータからの熱を前記被加熱体に向けて反射するためのリフレクタ14と、を備え、前記リフレクタは、前記ヒータを挟んで前記被加熱体とは反対側に配置され、前記リフレクタにおける前記開口部に近接する位置の面積を他の位置に比べて拡大した。

(もっと読む)

温度制御装置およびこの温度制御装置を備える真空処理装置

【課題】真空チャンバ内で対象物を直接に温度制御でき、熱効率が高く、かつ小型で簡易的な温度制御装置、およびこの温度制御装置を備えた真空処理装置を提供する。

【解決手段】この温度制御装置は、真空チャンバ11内に設置されかつ対象物を配置する伝熱ステージ12の温度を制御するための温度制御装置であって、ピストン機構部13Aと冷凍機冷却部13Bを有し、冷凍機冷却部を伝熱ステージに直接に接触させるように当該冷凍機冷却部が真空チャンバの内部に配置されるようにされた冷凍機13と、冷凍機の冷却運転動作を制御する制御部17とを備えるように構成される。また真空処理装置10はこの温度制御装置を備えるように構成される。

(もっと読む)

圧電体薄膜の製造方法及び圧電体薄膜の製造装置

【課題】圧電特性のばらつきが少ないチタン酸ジルコン酸鉛薄膜を効率よく製造する圧電体薄膜の製造方法を提供する。

【解決手段】チタン酸ジルコン酸鉛のターゲット3を使用し、スパッタ法により基板5の上にチタン酸ジルコン酸鉛薄膜を製造する圧電体薄膜の製造方法において、基板を加熱する基板加熱工程と、基板加熱工程で加熱した基板の温度を維持し、スパッタ法により基板の上に成膜する成膜工程と、を有し、基板加熱工程では、基板が所定の温度分布となるように加熱され、成膜工程では、基板と前記ターゲットとで挟まれる空間の、ターゲット面に平行な面の面内で、所定の酸素濃度分布となるように酸素が導入され、基板及び平行な面それぞれへターゲットの面を垂直投影した場合、基板と平行な面との相互に対応する位置における所定の温度分布の増減方向と所定の酸素濃度分布の増減方向とは同じ方向である。

(もっと読む)

蒸着装置

【課題】基材の温度制御を高精度に行い、蒸着する微粒子の粒径を所望の大きさにコントロールできる蒸着装置を提供する。

【解決手段】温度制御ユニット32は、温度制御された液体または固体の熱媒体が供給される伝熱ブロック34と、この伝熱ブロックの基材との対向面側に保持された伝熱ローラー36とを備える。この伝熱ローラーは、降下移動して基材の裏面に当接し、基材の移送に連動してこの移送方向と交差する軸を中心に回転するとともに、基材からの力で上昇移動が可能である。伝熱ローラーおよび伝熱ブロックは、基材と熱媒体との間で熱を伝播し、基材の温度を高精度に制御する。

(もっと読む)

表面被覆切削工具

【課題】基材上の被膜の密着性が高いとともに、優れた耐熱性と優れた耐摩耗性と優れた潤滑性とを併せ持つ表面被覆切削工具を提供する。

【解決手段】 本発明の表面被覆切削工具は、基材と、該基材上に形成された被膜とを備えるものであって、該被膜は、物理蒸着法により形成され、かつ一以上の層を含み、該一以上の層のうち少なくとも一層は、第1被膜層であり、該第1被膜層は、AlとNとを含み、その熱浸透率が2000J・sec-1・m-1・K-1以上5000J・sec-1・m-1・K-1以下であって、かつ0.2μm以上5μm以下の膜厚であり、第1被膜層は、基材側から順に非晶質領域と結晶質領域とを有し、非晶質領域は、非晶質からなり、かつ0.01μm以上2μm以下の厚みであり、結晶質領域は、六方晶構造を含む結晶構造からなることを特徴とする。

(もっと読む)

ロードロック室及びそれを備えた薄膜形成装置

【課題】 本発明は、基板の冷却効果及び、加熱効率を高めた、省スペースのロードロック室を提供する。

【解決手段】 ロードロック室は、未処理基板を搬入し、処理基板を搬入するロードロック室であって、ロードロック室内部の上方に設けられた基板加熱手段と、ロードロック室内部であって、かつ基板加熱手段の下方に対向配置された、基板冷却手段と、ロードロック室を区画するように設けられ、基板加熱手段に接近可能な第1ステージと、第1ステージに設けられ、基板を支持する複数の第1ピンと、基板冷却手段を備えた第2ステージと、前記第2ステージに設けられ、基板を支持する複数の第2ピンと、を備え、基板加熱手段によって基板を加熱する際には、第1ピンは第1ステージ内に収納されず、基板冷却手段によって基板を冷却する際には、第2ピンは第2ステージ内に収納されることを特徴とする。

(もっと読む)

成膜装置および成膜方法

【課題】水と反応すると危険な成膜原料で薄膜を形成する際、安全に成膜を実施できる成膜装置、および成膜方法を提供する。

【解決手段】成膜対象である基材9を内部に収納する真空チャンバー2と、真空チャンバー2内で基材9を保持するホルダー4と、ホルダー4に対向する位置に設けられる蒸発源3と、ホルダー4内に冷媒を循環させる循環機構40とを備える成膜装置1である。そして、この成膜装置1においてホルダー4内に循環される冷媒を非水系冷媒とする。このような構成とすることで、ホルダー4に保持される基材9を冷却しつつ、蒸発源3で蒸発させた成膜原料を基材9の表面に成膜することができ、その成膜の際に安全性を確保することができる。

(もっと読む)

ZnOターゲットおよびその製造方法

【課題】 DCスパッタリングでも高抵抗なZnO膜を作製可能なZnOターゲットおよびその製造方法を提供すること。

【解決手段】 ZnOターゲットが、ZnOを主成分とし、不可避不純物が0.1質量%以下であり、ZnO粒子の平均粒径が、15μmから100μmである。このZnOターゲットの作製方法は、ZnO粉末を、3.0g/cm3以上の密度に成形して成形体とする工程と、成形体を、1200℃から1500℃の焼結温度で焼成して焼結体とする工程と、を有している。

(もっと読む)

長期成膜時の安定性に優れたIn−Ga−Zn−O系酸化物焼結体スパッタリングターゲット

【課題】長期に渡る成膜を行った際に、得られる薄膜の特性の安定性に優れたスパッタリングターゲットを提供する。

【解決手段】In、Zn、及びGaを含み、表面と内部の化合物の結晶型が実質的に同一である酸化物焼結体からなり、下記(a)〜(e)の工程で製作されたスパッタリングターゲット。(a)原料化合物粉末を混合し、調製(b)混合物6.0mm以上に成形(c)3℃/分以下で昇温(d)1280〜1520℃で2〜96時間(e)表面を0.25mm以上研削

(もっと読む)

圧電体素子およびインクジェット式記録ヘッド

【課題】製造中に膜内にクラックの発生がなく、高い圧電ひずみ定数を有し、下電極との密着性が良い圧電体薄膜素子、および、この圧電体薄膜素子を用いた高精細な印字が可能となるインクジェット記録ヘッドを提供する。

【解決手段】多結晶体からなる圧電体膜11Aと、この圧電体膜11Aを挟んで配置される上電極16と下電極12と、を備えた圧電体薄膜素子であって、圧電体膜の結晶体11Aが、電極面に対して略垂直方向に形成される。

(もっと読む)

成膜装置および強誘電体膜の製造方法

【課題】基板の温度制御変動を抑制し、高品質の膜を再現性よく成膜することのできる成膜装置を提供する。

【解決手段】蒸発源12およびプラズマ生成空間と、基板保持部に保持された基板14とをシャッター20で隔てた状態で、蒸発源を加熱し、プラズマ105を生成する。基板サセプタ13に内蔵された加熱源13aにより基板を加熱するとともに、シャッターの基板側の面に配置された輻射熱源により、蒸発源およびプラズマからシャッターに到達している熱量と同等の輻射熱量を供給して基板を加熱する。基板の温度が所定の温度に達した状態で、シャッターを開き、蒸発源からの蒸気をプラズマを通過させて、基板上に堆積させる。これにより、シャッターを開いても基板温度の変動を抑制できる。

(もっと読む)

静電チャックを備えた基板ホルダを用いた基板温度制御方法

【課題】200〜500℃の温度範囲で、高速かつ高精度に基板温度を制御可能な基板温度制御を提供する。

【解決手段】本発明の基板ホルダを用いた基板温度制御方法は、

(1)基板のプロセス開始前に、静電チャック3上の基板10を第1の設定温度まで昇温させる第1の行程と、

(2)基板10のプロセス開始時に、静電チャック3上の基板10を第1の設定温度より高い第2の設定温度まで昇温させる第2の行程と、

(3)基板10のプロセス中に、第2の設定温度まで加熱された基板10を第1の設定温度まで降温させる第3の行程と、

(4)基板10のプロセス終了まで、基板10を第1の設定温度に維持する第4の行程と、

を含むことを特徴とする。

(もっと読む)

表面被覆切削工具の製造方法

【課題】導電性を有する酸化物膜を基材表面上に成膜することにより耐酸化性、耐欠損性、耐摩耗性の全てに優れ、また、物理蒸着法により成膜可能であり、さらに美しい外観色を呈することにより商品価値の高い表面被覆切削工具の製造方法を提供する。

【解決手段】基材上にコーティング層を備える表面被覆切削工具の製造方法であって、前記コーティング層は、前記基材側から内層および外層をこの順で備え、該内層は、周期律表4a族に属する金属、5a族に属する金属、6a族に属する金属、AlおよびSiからなる群より選択される1種以上の元素と、炭素、窒素および酸素からなる群より選択される1種以上の元素との化合物から構成され、前記外層は、導電性を有する酸化物膜から構成される表面被覆切削工具の製造方法を提供する。

(もっと読む)

高アスペクト比凹凸形状に薄膜を成膜する方法

【課題】短時間かつ低コストな高アスペクト比凹凸形状の薄膜形成方法を提供すること。

【解決手段】基板表面に成膜する過程で当該基板を加熱することでマイグレーション現象により複数の成膜粒子を移動集合させて薄膜単位を形成し、これら複数の薄膜単位により基板表面に高アスペクト比凹凸形状の薄膜パターンを形成する。

(もっと読む)

121 - 140 / 495

[ Back to top ]