Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

1,981 - 2,000 / 3,070

ショットキバリアダイオードおよびエピタキシャル基板

【課題】オン抵抗の上昇を抑える共に、リーク電流を低減することが可能なショットキバリアダイオードの提供。

【解決手段】導電性III族窒化物基板13は、第1の面13aおよび第2の面13bを有する。また、導電性III族窒化物基板13は、1×106cm−2以下の転位密度D13を有する。n型窒化ガリウム系半導体ドリフト層15は、基板13の第1の面13a上に設けられており、また1×1017cm−3以下のキャリア濃度N15を有する。第1のn型窒化ガリウム系半導体層17は、n型窒化ガリウム系半導体ドリフト層15上に設けられており、また0.5×1017cm−3以下のキャリア濃度n17を有する。ショットキ電極19は、第1のn型窒化ガリウム系半導体層17にショットキ接合を成す。オーミック電極21は、基板13の第2の面上に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 仕事関数が調節され、ゲート抵抗が低いシリサイドゲート電極を有する半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板11に形成されたp型ウェル領域13と、p型ウェル領域13上に形成された第1ゲート絶縁膜17と、第1ゲート絶縁膜17上に、NiSi2を主成分とする第1シリサイド膜18aと、導電膜18bと、NiSiを主成分とする第2シリサイド膜18cとがこの順に形成された第1ゲート電極18と、第1ソース・ドレイン領域19、20とを備えたn−MOSトランジスタ15と、p型ウェル領域13と離間して形成されたn型ウェル領域14と、n型ウェル領域14上に形成された第2ゲート絶縁膜21と、第2ゲート絶縁膜21上に形成され、NiSiを主成分とする第3シリサイド膜22aを有する第2ゲート電極22と、第2ソース・ドレイン領域23、24とを備えたp−MOSトランジスタ16とを具備する。

(もっと読む)

めっき処理ユニット

【課題】めっき処理を品質良く確実に行えるばかりでなく、装置全体のコンパクト化や、装置コストの低廉化が図れるめっき処理ユニットを提供する。

【解決手段】処理槽内部に吸着ヘッド789で保持した基板Wを挿入した状態で基板Wの処理面にめっき液による接液処理を行うめっき処理ユニットであって、吸着ヘッド789は、基部791の下面外周に基板Wの裏面をリング状に真空吸着すると共に基板Wの裏面の真空吸着した部分の内側へのめっき液の浸入を防止してシールするリング状の基板吸着部795を取り付けて構成され、基部791には、基板吸着部795に吸着した基板Wと基部791の間の空間を開放する開口部が設けられている。

(もっと読む)

中間層を有する半導体素子の形成方法及びその構造

基板(10)上に位置するスタック(30)。スタックは、誘電体層(16)と金属層(26)との間に層(24)を有する。その層は、ハロゲン及び金属を含む。一実施形態において、ハロゲンはフッ素である。一実施形態において、スタックは、トランジスタ用の制御電極スタックである。一例において、制御電極スタックは、MOSFET用のゲートスタックである。一例において、層はフッ化アルミニウムを含む。  (もっと読む)

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

導電体の作製方法

【課題】多孔質の紙及びポリマー基材上又は半導体表面上に低い電気抵抗をもつ導電性のライン及び表面パターンを作製する技術を提供する。

【解決手段】基材上に導電体を作製する方法であって、金属粒子、金属前駆体及びそれらの混合物からなる群から選択された少なくとも1種の成分で構成された導体配合物を基材上に塗布する工程、該導体配合物を負に帯電したイオン性の還元性ガスに曝露しながら、焼結により該成分を金属に変えそして導電体を作製する工程、を含む。

(もっと読む)

シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体

【課題】シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体を提供する。

【解決手段】上に配置される少なくとも1つの電界効果トランジスタを含み、前記少なくとも1つの電界効果トランジスタに隣接して配置されるシリサイド・コンタクト領域16A,16B,16Cを含む、半導体基板12と、前記半導体基板上に配置され、前記少なくとも1つの電界効果トランジスタの上に延び、前記シリサイド・コンタクト領域を露出させるコンタクト開口部20を有する絶縁中間層18と、前記コンタクト開口部内の金属ゲルマニウム化物含有コンタクト材料24とを備える。

(もっと読む)

II−VI族半導体光変換素子内のオーミック接触のパッシベーションキャップ層

【課題】II-VI族半導体素子において、多層コンタクト層の最表面BeTe層の酸化を防止する。

【解決手段】II-VI族半導体素子は、半導体層10のスタックを含む。オーミク接触34が提供され、このスタックに電気的に結合する。このオーミック接触は、酸化性物質に暴露されるときに、ある酸化速度を有する。パッシベーションキャップ層42は、オーミック接触の上に重なり、オーミック接触の酸化速度よりも小さい酸化速度を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホールを有する半導体装置及びその製造方法において、ビアホール内におけるバリア層の被覆不足防止とビア抵抗を制御することの両者を同時に達成することを目的とする。

【解決手段】その表面上にパッド電極3を有する半導体基板1を準備する。次に、半導体基板1の裏面から表面方向にエッチングし、パッド電極3を露出させるビアホール8を形成する。次に、スパッタリング法またはPVD法、及び逆スパッタリング(エッチング)によりビアホール8内に第1のバリア層11を形成する。この逆スパッタリングによりビアホール8底部のバリア層が除去され、パッド電極3が露出される。次に、ビアホール内で露出したパッド電極3上に第2のバリア層12を形成する。第2のバリア層12の膜厚のみを調節することでビア抵抗を制御する。

(もっと読む)

電解処理装置及びその電場状態制御方法

【課題】積極的に被処理基板表面の電場状態を制御することで、目的とするめっき膜厚の面内分布が得られる電解処理装置及びその電場状態制御方法を提供すること。

【解決手段】陽極38と被処理基板W間にめっき液10を満たし、且つ陽極38と被処理基板W間にめっき液10の電気伝導率よりも低い電気伝導率の高抵抗構造体4を設置する。高抵抗構造体4の厚みの調整や、高抵抗構造体4の平面上での形状の調整等により、被処理基板W表面の電場を制御する。

(もっと読む)

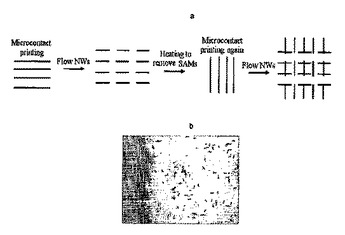

ナノスケール電子素子製造のための表面上へのナノワイヤのパターン形成

本発明は、基板の規定された領域に、基板表面と結合でき且つナノワイヤと結合できる少なくとも1つの化合物(C1)を接触させて、基板表面上に結合サイトのパターンを提供し、および/または基板の規定された領域に、基板表面と結合し且つナノワイヤの結合を阻止する少なくとも1つの化合物(C2)を接触させて、基板表面上に非結合サイトのパターンを提供し、且つ、基板表面を液体媒体中のナノワイヤの懸濁液と接触させて適用したナノワイヤの少なくとも一部分を、(C1)で被覆されている、および/または(C2)で被覆されていない基板表面の少なくとも一部分と結合させる工程を含む、基板表面へのナノワイヤの堆積方法に関する。  (もっと読む)

(もっと読む)

金属/半導体/金属の積層構造を有する双方向ショットキーダイオード及びその形成方法

【課題】 金属/半導体/金属の積層構造の双方向ショットキーダイオードの形成方法を提供する。

【解決手段】 下部電極104と上部電極114との間に挟持されるシリコン半導体層110を堆積する工程と、閾値電圧、降伏電圧、及び、オン/オフ電流比を有する双方向ショットキーダイオードを形成する工程と、双方向ショットキーダイオードの閾値電圧、降伏電圧、オン/オフ電流比をシリコン半導体層の膜厚112の制御によって調整する工程と、を備える。閾値電圧と降伏電圧は何れもシリコン半導体層の膜厚の増加に従って増加する。オン/オフ電流比に対してシリコン半導体層の最適膜厚が存在する。化学気相成長法またはDCスパッタリング法を用いて非晶質シリコンまたは多結晶シリコンの半導体層を形成する。シリコン半導体層はV族のドナー材料でドーピングできる。当該ドーピングによって閾値電圧は減少し、降伏電圧は増加する。

(もっと読む)

クラスタ処理装置

【課題】酸化物形成から完全に鋼層を保護することができるクラスタ処理装置を提供する。

【解決手段】筐体200と、少なくとも1つの処理チャンバ210と、ロボット220と、少なくとも1つのバルブ230,240と、を備える。筐体200は、筐体内にガスを含むとともに、筐体の開口部に蓋をするように構成された少なくとも1つの扉203を備える。ガスは、少なくとも1つの還元ガスを含む。ロボット220は、筐体200内に設けられるとともに、扉203と処理チャンバ210との間で基板270を搬送するように構成されている。バルブ230,240は筐体200へ接続される。

(もっと読む)

成膜装置及び成膜方法

【課題】マンガン膜をCVD法により形成することができる成膜装置を提供する。

【解決手段】被処理体Wの表面にマンガン膜をCVD(Chemical Vapor Deposition)により形成する成膜装置において、真空引き可能になされた処理容器14と、前記処理容器内に設けられて前記被処理体を載置するための載置台16と、前記処理容器内へマンガンが含有された有機金属材料或いは金属錯体材料を含む原料ガスを供給する原料ガス供給手段18と、前記処理容器内へ還元ガスを供給する還元ガス供給手段20とを備える。これにより、マンガン膜をCVD法により形成する。

(もっと読む)

自己整合した耐熱性コンタクトを備える半導体デバイス及びその作製方法

半導体デバイスを形成する方法が、半導体基板上に半導体層を形成することによって提供される。マスクが、半導体層上に形成される。半導体層上に複数のイオン注入領域を形成するために、第1の伝導型を有するイオンがマスクによって半導体層中へ注入される。マスクによってイオン注入領域上に金属層が形成される。複数のイオン注入領域に注入されたイオンをそれぞれ活性化し、かつ複数のイオン注入領域上にオーミックコンタクトを設けるために、複数のイオン注入領域および金属層が単一工程でアニールされる。関連するデバイスも提供される。  (もっと読む)

(もっと読む)

配線および有機トランジスタとその製法

【課題】塗布による安価な有機トランジスタを作成しようとするとき、安価な電極材料では半導体との接触抵抗が大きく、接触抵抗の小さい電極材料は高価であるという問題がある。これを解決するために、材料費も製造コストも安価に済み、且つ半導体との接触抵抗が小さい高性能な有機トランジスタ及びその製造方法を提供すること。

【解決手段】電極本体は主に安価な第1の金属で作成し、その表面を高価だが高性能な第2の金属の薄膜で覆う構造を作成する。この構造を安価に安定に得るために、第1の金属と第2の金属の合金において第2の金属が表面偏析しやすいという性質を利用する。

(もっと読む)

銅の無電解堆積のためのメッキ溶液

【課題】

【解決手段】無電解銅メッキ溶液を開示する。溶液は、水性銅塩成分と、水性コバルト塩成分と、トリアミンに基づく錯化剤と、無電解銅メッキ溶液を酸性にするのに十分な量の酸性pH修飾物質とを含む。無電解銅溶液を調製する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留りを向上する。

【解決手段】半導体ウエハ1にウエハ・プロセスを施した後に再配線を施してから、半田印刷用のマスク32を用いて半導体ウエハ1の端子23上に半田ペースト31を印刷法で供給する。その後、半田リフロー処理により半田バンプを形成してから、半導体ウエハ1をダイシングして、半導体チップを製造する。半田印刷に用いるマスクは、半導体ウエハ1に接する側の主面32aの表面粗さを0.3μm以下とし、マスク32のテンションを700μm〜900μmとしている。

(もっと読む)

CMOSトランジスタゲートにおいてリセスされた仕事関数金属

トランジスタゲートは、表面上に配置された一対のスペーサを有する基板と、スペーサ間で基板上にコンフォーマルに堆積された高k誘電体と、高k誘電体上とスペーサの側壁の一部に沿ってコンフォーマルに堆積されたリセスされた仕事関数金属と、リセスされた仕事関数金属上にコンフォーマルに堆積された第2の仕事関数金属と、第2の仕事関数金属上に堆積された電極金属とを含む。トランジスタゲートは、高k誘電体を基板上のスペーサ間にあるトレンチ内にコンフォーマルに堆積し、高k誘電体上に仕事関数金属をコンフォーマルに堆積し、仕事関数金属上に犠牲マスクを堆積し、仕事関数金属の一部を露出すべく犠牲マスクの一部をエッチングし、リセスされた仕事関数金属を形成すべく仕事関数金属の露出された一部をエッチングすることにより形成されうる。第2の仕事関数金属及び電極金属が、リセスされた仕事関数金属上に堆積されうる。 (もっと読む)

金属膜のエッチング方法及び半導体装置の製造方法

【課題】金属膜に設けられる下層の高誘電率材の薄膜をエッチングすることなく、金属膜を1層又は数層毎に少しずつエッチングする金属膜のエッチング方法及びこれをもちいる半導体装置の製造方法である。

【解決手段】半導体基板10上のゲート12を形成する工程が、前記金属膜21にハロゲン原子のイオン又はラジカルに電気的バイアスを印加せずに金属膜21に吸着させる第1工程と、酸素を含みイオン又はラジカルに電気的バイアスを印加してエッチングする第2工程とを有する金属膜のエッチング方法及び半導体装置10の製造方法である。この半導体の製造方法は、第1工程と第2工程の双方を有することで、下地に高誘電率材のゲート用の絶縁層22のエッチングを抑えることができる。

(もっと読む)

1,981 - 2,000 / 3,070

[ Back to top ]