Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

1,961 - 1,980 / 3,070

金属配線形成方法

【課題】下地層と導電層との密着性を向上させた金属配線形成方法を提供すること。

【解決手段】基板S上に形成されたマンガン層25上に、金属微粒子を分散させた配線形成用インクX2を塗布する第2液滴吐出工程と、配線形成用インクX2を加熱して前記金属微粒子を粒成長させて銀層26を形成する第2焼成工程とを有し、前記第2焼成工程で、焼成温度までの平均昇温速度が、20℃/分以上200℃/分以下である。

(もっと読む)

低ホットキャリア効果を具えた半導体構造

【課題】半導体のトランジスタ構造の操作時に「ホットキャリア効果」の程度を低減し、該トランジスタを具えたOLED駆動ICの使用寿命を延長可能な低ホットキャリア効果を具えた半導体構造の提供。

【解決手段】基板、金属層、絶縁層、第一半導体層、第二半導体層を含む。該第一半導体層は第一電気抵抗値を具え、少なくとも該絶縁層の部分表面を覆い、該第二半導体層は第二電気抵抗値を具え、少なくとも該絶縁層の部分表面を覆蓋する。該第二半導体層の第二電気抵抗値は該第一半導体層の第一電気抵抗値より大きい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極を埋め込み形成する際の埋め込み特性を改善する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2を介して、第1ゲート電極層3aと第2ゲート電極層3bとをこの順に積層してなるゲート電極3を形成する半導体装置の製造方法であって、まず、半導体基板1上に、ゲート絶縁膜2と、ゲート電極3の仕事関数を規定する金属含有材料からなる第1ゲート電極層3aとをこの順に積層する工程を行う。次に、第1ゲート電極層3a上に、第1ゲート電極層3aに達する凹部8を有する絶縁層7を形成する工程を行う。次いで、凹部8に、第1ゲート電極層3aよりも抵抗値の低い金属含有材料からなる第2ゲート電極層3bを埋め込む工程を行う。その後、第2ゲート電極層3bをマスクとして、第1ゲート電極層3aをパターンニングする工程を行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

半導体ウェハーの前処理剤及び前処理方法

【課題】銅シード層を設けた半導体ウェハーの、トレンチ・ビアの入り口付近に過剰に付着した銅シード層を溶解し、その後電気銅めっき、無電解銅めっきによるネッキングを防止し、トレンチ・ビア内部の完全な埋め込みが可能となる前処理剤を提供することを目的とする。

【解決手段】アンモニウムイオン濃度が0.1g/L以上で、pHが11以上であることを特徴とするシード層を有する半導体ウェハーの前処理剤。該前処理剤は、金属イオンを含有しないことが好ましく、更に界面活性剤を含有することが好ましい。

(もっと読む)

前面発光型窒化物系発光素子の製造方法

【課題】前面発光型窒化物系発光素子の製造方法を提供する。

【解決手段】基板10上に順次積層されたn型クラッド層30、活性層40、p型クラッド層50及び透明導電性薄膜層60を備え、ここで、透明導電性薄膜層60は、内部で発生した光の外部発光効率を高めるために別途のエッチングマスクなしに湿式エッチング方式とポスト熱処理によるナノメートルスケールでパターニングされた表面を有する窒化物系発光素子である。これにより、湿式エッチングとポスト熱処理法により形成されたパターニングされた表面を有する透明導電性薄膜層を介して素子の外部発光効率を極大化させることができ、高輝度発光ダイオードの具現を可能にする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CVD法により上部電極を成膜する際の下地層へのダメージを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板11上の層間絶縁膜16に設けられた凹部17の内壁を覆う状態で、層間絶縁膜16上にゲート絶縁膜18を形成する工程と、ゲート絶縁膜18上に、仕事関数を制御する第1ゲート電極層19aを形成する第1工程と、第1ゲート電極層19a上に、下地層へのバリア性を有する第2ゲート電極層19bを形成する第2工程と、第2ゲート電極層19bが設けられた凹部17を埋め込む状態で、第2ゲート電極層19b上に、化学的気相成長法により、第1ゲート電極層19aよりも抵抗の低い第3ゲート電極層19cを形成する第3工程とを行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

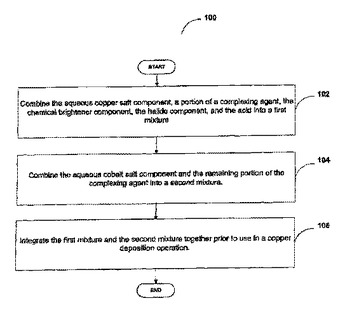

銅の無電解析出のためのめっき溶液

本明細書では無電解銅めっき溶液を開示する。この溶液は、水性銅塩成分と、水性コバルト塩成分と、ポリアミン系錯化剤と、化学光沢剤成分と、ハロゲン化物成分と、この無電解銅めっき溶液を酸性にするのに十分な量のpH調整物質とを含む。また、無電解銅溶液を調製する方法も提供する。水性銅塩成分は、硫酸銅(II)、硝酸銅(II)、塩化銅(II)、テトラフルオロホウ酸銅(II)、酢酸銅(II)、エチレンジアミン硫酸銅(II)、ビス(エチレンジアミン)硫酸銅(II)、およびジエチレンアミン硝酸銅(II)からなる群から選択され得る。  (もっと読む)

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法

【課題】本発明は、液晶表示装置用アレイ基板に係り、より詳しくは、有機半導体物質を半導体層とする液晶表示装置用アレイ基板及びその製造方法に関する。

【解決手段】本発明は、基板上に金属物質で構成されて、相互に離隔して形成された第1ソース電極及び第1ドレイン電極と;透明導電性物質で構成されて、前記第1ソース電極及び前記第1ドレイン電極の上部面を覆う第2ソース電極及び第2ドレイン電極と;前記第2ドレイン電極と接触する画素電極と;前記基板上に形成された有機半導体層と;前記基板上に形成されたゲート絶縁膜と;前記基板上に形成されたゲート電極とを含むことを特徴とする液晶表示装置用アレイ基板を提供する。

(もっと読む)

成膜方法及び成膜装置

【課題】基板にダメージを与えることなく、基板の表面にシード膜等の薄膜を均一に成膜できるようにする。

【解決手段】金属またはその化合物とカルボン酸とをカルボン酸蒸気を含む雰囲気下で加熱反応させ、金属またはその化合物とカルボン酸との反応生成物を飛散させて、金属またはその化合物からなる薄膜を基板の表面に成膜する。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することができる技術を提供する。

【解決手段】主面100a(第1主面)と、主面100bの反対側に位置する主面100b(第2主面)とを有し、主面100b側に一部が露出するように形成された導電層1(第1導電層)および導電層2(第2導電層)と、導電層1の主面1aに電気的に接続されるLEDチップ4(発光半導体チップ)と、LEDチップ4と導電層2を電気的に接続するワイヤ5(導電性部材)と、導電層1、導電層2、ワイヤ5およびLEDチップ4を封止する透光性の封止体3とを備え、主面100a上には集光レンズを形成せず、導電層1、導電層2、ワイヤ5およびLEDチップ4は封止体3のみにより封止されるように構成する。

(もっと読む)

成膜方法および成膜装置、ならびに記憶媒体

【課題】ステップカバレッジが良好で、原料を安定的に供給するとともに原料の劣化を生じさせずに実用的かつ安価に良質な金属膜を成膜することができる成膜方法および成膜装置を提供する。

【解決手段】カルボン酸と酸素含有金属化合物とを反応させてカルボン酸塩ガスを生成する工程と、基板1上にカルボン酸塩ガスを供給してカルボン酸塩膜2を堆積させる工程と、カルボン酸塩膜2が堆積された基板1にエネルギーを与えてカルボン酸塩膜2を分解して金属膜3を形成する工程とを有する。

(もっと読む)

導電薄膜及びその製造方法

【課題】電極として用いることが可能な金属を含む導電薄膜を、表面の凹凸が少ない状態で形成できるようにする。

【解決手段】導電薄膜103は、例えば単結晶シリコンからなる基板101の上に、例えば、アモルファス状態のシリコン酸化膜よりなる下部絶縁膜102を介して形成されたものである。導電薄膜103は、ルテニウムと窒素から構成されたものである。導電薄膜103は、ルテニウムよりなるターゲットを、アルゴンガス(Ar)、キセノン(Xe)ガス、窒素ガスからなるECRプラズマを用いてスパッタリングして形成すればよい。

(もっと読む)

支持体上に導電性の表面を製造する方法

導電性の、構造化された、又はほぼ平坦な表面を支持体上に製造する方法であって、第1工程で、マトリックス材料中に導電性の粒子を含む分散物を使用して、構造化された又はほぼ平坦な基礎層を支持体上に施し、第2工程で、マトリックスを少なくとも部分的に硬化及び/又は乾燥させ、第3工程で、マトリックスを少なくとも部分的にブレークすることによって導電性の粒子を露出させ、そして第4工程で、無電解及び/又は電解被覆によって、構造化された又はほぼ平坦な基礎層上に金属層を形成することを特徴とする方法。 (もっと読む)

銅相互接続層用の無電解NiP接着及び/又はキャップ層

銅相互接続層を、例えばTFT−LCDフラットパネル相互接続システムにおいて使用されるガラス基板などの基板上に堆積させる方法。本発明に従う方法は、a)任意に、基板を清浄化する工程と、b)任意に、この基板をミクロエッチングする工程と、c)触媒化層を基板上に堆積させて、触媒化基板を得る工程と、d)触媒化基板を、調整溶液を用いて調整して、調整触媒化基板を得る工程と、e)前記基板又はまたはその少なくとも一部をNi及びPの前駆体を含んだウェッツバス混合物と接触させることによって、前記触媒化基板に無電解NiP層を鍍金して、NiP鍍金調整触媒化基板を得る工程と、f)銅用触媒層をNiP鍍金層上に堆積させる工程と、g)Cu層を前記銅用触媒層上に堆積させる工程とを含んでいる。 (もっと読む)

液晶表示装置における配線および電極用銅合金薄膜並びにその薄膜を形成するためのスパッタリングターゲット

【課題】液晶表示装置の配線および電極を形成するための銅合金薄膜並びにその薄膜を形成するためのスパッタリングターゲットを提供する。

【解決手段】B:5〜2000wtppmを含み、残部がCuおよび不可避不純物からなる組成を有する液晶表示装置の配線および電極用銅合金薄膜およびその薄膜を形成するためのスパッタリングターゲット。

(もっと読む)

半導体装置、電気光学装置、電子機器及び半導体装置の製造方法

【課題】使用するアクティブマトリクス方式の表示器に使用される有機半導体装置においてゲート駆動信号を伝搬するゲート線(ゲート信号線)の抵抗値を下げることを可能とした半導体装置、電気光学置及び電子機器を提供する。

【解決手段】基板上(101)に形成された有機半導体トランジスタと、有機半導体トランジスタのソース又はドレイン電極(105)と接続されるデータ線(107)と、データ線と交差するように配置されて有機半導体トランジスタのゲート電極(110)に接続されるゲート線と、を備え、ゲート線は、ゲート電極(110a)、ゲート電極に信号を伝搬する第1のゲート線(102)、及びデータ線と層間絶縁層(109)を介して交差する第2のゲート線(110b)を含み、上記ゲート電極、上記第1及び第2のゲート線は互いに直列に接続され、第1のゲート線(102)の導電率がゲート電極(110a)及び第2のゲート線(110b)の導電率よりも高い、ことを特徴とする。

(もっと読む)

実効仕事関数を調整するための方法

【課題】本発明は、様々なトランジスタタイプの金属ゲート電極の実効仕事関数及び閾値電圧を、簡便で、再生可能でまた効率的な方法で制御することができるMOSFETデバイスを製造する方法を提供すること。

【解決手段】本発明は、MOSFET、FinFET、若しくはメモリーデバイスにおけるゲートを作製するにあたり、半導体基板上に、(予め)決定された移動度、リーク、及び/又はEOT(酸化膜換算膜厚)の仕様を満たす誘電体材料からなる少なくとも一層を成長させ、

上記ゲート電極を形成する前に、上記少なくとも一層の誘電体層とゲート電極との間の界面に、ランタンハフニウム酸化物材料を含む若しくはこれからなる、好ましくはLa2Hf2O7からなる界面層を成長させ、上記界面層に接触する誘電体材料からなる少なくとも一層を、上記界面層材料と相違させることを特徴とする。

金属ゲート電極、ゲート誘電体及び界面層を備える新たなMOSFETを開示している。その製造方法、及びその応用も提供する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース電極及びドレイン電極のコンタクト抵抗が小さく且つ電極の形成が容易な電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板10の上に形成され、一般式がInxAlyGa1−yN(0<x≦1、0≦y<1、0<x+y≦1)で表されるキャップ層25を含む窒化物半導体積層体20と、キャップ層25の上に互いに間隔をおいて形成されたノンアロイのソース電極31及びノンアロイのドレイン電極32とを備えている。

(もっと読む)

半導体整流素子

【課題】本発明は、順方向バイアス印加時におけるオン抵抗の増加を抑制しながら、逆方向バイアス時におけるリーク電流を抑制して耐圧の低下を抑制することができる半導体整流素子を提供する。

【解決手段】ショットキー電極50は、隣り合う電界緩和層40の間に位置し、かつドリフト層30の表面上に接触するようにして形成された第1の領域50Bと、ショットキー電極のうち第1の領域を除く第2の領域50Aとを有し、第1の領域は、第2の領域よりバリアハイトが高い導電性材料によって形成されている。

(もっと読む)

実効仕事関数を調整するための方法

【課題】本発明は、様々なトランジスタタイプの金属ゲート電極の実効仕事関数及び閾値電圧を、簡便で、再生可能でまた効率的な方法で制御することができるMOSFETデバイスを製造する方法を提供すること。

【解決手段】本発明は、MOSFET、FinFET、若しくはメモリーデバイスにおけるゲートを作製するにあたり、半導体基板上に、(予め)決定された移動度、リーク、及び/又はEOT(酸化膜換算膜厚)の仕様を満たす誘電体材料からなる少なくとも一層を成長させ、

上記ゲート電極を形成する前に、上記少なくとも一層の誘電体層とゲート電極との間の界面に、ランタンハフニウム酸化物材料を含む若しくはこれからなる、好ましくはLa2Hf2O7からなる界面層を成長させ、上記界面層に接触する誘電体材料からなる少なくとも一層を、上記界面層材料と相違させることを特徴とする。

金属ゲート電極、ゲート誘電体及び界面層を備える新たなMOSFETを開示している。その製造方法、及びその応用も提供する。

(もっと読む)

1,961 - 1,980 / 3,070

[ Back to top ]