Fターム[4M104DD45]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | CVD (2,824) | 原料ガス (770)

Fターム[4M104DD45]に分類される特許

21 - 40 / 770

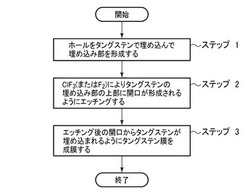

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

成膜装置及び成膜方法

【課題】 タングステン膜を成膜する際に半導体ウェーハがエッチングされることを抑制する成膜装置及び成膜方法を提供することである。

【解決手段】 実施形態に係る成膜装置は、半導体ウェーハを載置するためのステージと、前記ステージ上に載置される半導体ウェーハの周縁部を覆うように配置されるエッジカット部を備え、前記半導体ウェーハ上にタングステン膜を成膜する。前記エッジカット部は、前記半導体ウェーハの周縁部と接触可能に設けられた第1のエッジカット部と、前記第1のエッジカット部に接続され、前記半導体ウェーハと実質的に垂直な方向に上下動可能な接続部と、前記接続部に接続され、前記接続部の上下動により前記半導体ウェーハの内側面に当接するように配置された第2のエッジカット部と、を備える。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 より平滑な表面を持ち、かつ、更なる薄膜化を達成することが可能なアモルファスシリコン膜の成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを供給し、下地2表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2表面のシード層3にアミノ基を含まないシラン系ガスを供給し、シード層3上にアモルファスシリコン膜4を、層成長する厚さに形成する工程と、層成長する厚さに形成されたアモルファスシリコン膜4をエッチングし、該アモルファスシリコン膜4の膜厚tを減ずる工程とを備える。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】反応管が石英で構成されたホットウォール型の基板処理装置においても、基板上にタングステン含有膜を生産性よく形成することのできる基板処理技術を提供する。

【解決手段】石英で構成された反応管内に基板が搬入されてない状態で、前記反応管内を加熱するとともに、前記反応管内にチタン含有ガスと窒素含有ガスとを供給して前記反応管の内壁に窒化チタン膜をプリコートする工程と、前記プリコート後の前記反応管内に基板を搬入する工程と、前記反応管内に基板が搬入された状態で、前記反応管内を加熱するとともに、前記反応管内にタングステン含有ガスを供給して前記基板上にタングステン含有膜を形成する工程と、前記タングステン含有膜を形成した基板を、前記反応管内から搬出する工程と、を行うようにした。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

酸化モリブデンを含有する薄膜の製造方法、酸化モリブデンを含有する薄膜の形成用原料及びモリブデンアミド化合物

【課題】CVD法による酸化モリブデンを含有する薄膜の製造においてプレカーサの輸送性に優れ、基板への供給量の制御が容易かつ安定供給が可能であり、量産性良く良質な酸化モリブデンを含有する薄膜を製造できる方法を提供すること。

【解決手段】下記一般式(I)で表される化合物を含有してなる薄膜形成用原料を気化させて得たモリブデンアミド化合物を含有する蒸気を基体上に導入し、さらに酸化性ガスを導入することで分解及び/又は化学反応させて基体上に薄膜を形成する、酸化モリブデンを含有する薄膜の製造方法。式中、R1、R2は炭素数1〜4の直鎖又は分岐状アルキル基を表し、R3はt−ブチル基又はt−アミル基を表し、yは0又は2を表し、xはyが0のときに4であり、yが2のときに2であり、複数存在するR1、R2はそれぞれ同一でもよく、異なっても良い。 (もっと読む)

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

Cu膜の形成方法

【課題】バリアメタル膜とCu膜との密着性を向上する。

【解決手段】基板上に、スパッタ法によりバリアメタル膜としてTi膜又はTa膜を形成し、このバリアメタル膜上にスパッタ法により窒化物膜を形成し、この窒化物膜の上にCVD法によりCu膜を形成した後、100〜400℃でアニール処理を行う。このようにCu膜を形成することにより、バリアメタル膜とCu膜との密着性が向上する。

(もっと読む)

NiSi膜の形成方法、シリサイド膜の形成方法、シリサイドアニール用金属膜の形成方法、真空処理装置、及び成膜装置

【課題】 トレンチ及びホールパターンの底面や、側面に被覆カバレッジ性の良好なシリサイド膜を形成できるNiSi膜の形成方法及びシリサイド膜の形成方法、シリサイドアニール用金属膜の形成方法、真空処理装置、並びに成膜装置の提供。

【解決手段】Siを主組成とする基板上にNi膜を形成し、このNi膜を加熱処理することにより基板の上層にNiSi膜を形成する方法であって、NiSi膜を形成する加熱処理の前に、その加熱処理温度よりも低く、NiSi膜が形成されない温度で、H2ガスを用いてNi膜をプレアニールしてNi膜中の不純物を除去し、次いで得られたNi膜をシリサイドアニールする。シリサイド膜を形成する前にプレアニールするためのプレアニール用のH2ガスを導入する手段を備えた装置。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

窒化チタン膜の形成方法、窒化チタン膜の形成装置及びプログラム

【課題】下地膜のエッチングを防止することができる窒化チタン膜の形成方法、窒化チタン膜の形成装置及びプログラムを提供する。

【解決手段】窒化チタン膜の形成方法では、まず、半導体ウエハWを収容した反応管2内を、昇温用ヒータ7により200℃〜350℃に加熱する。続いて、反応管2内にチタン原料を含む成膜用ガスを供給して半導体ウエハWに窒化チタン膜を形成する。このチタン原料には、塩素原子を含まず、チタンを含むメチルシクロペンタジエニルトリス(ジメチルアミノ)チタニウムを用いる。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

21 - 40 / 770

[ Back to top ]