Fターム[5E082FG03]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 気体・固体誘電体 (7,068) | 気体・固体誘電体の形状、構造 (2,216) | 薄膜 (375)

Fターム[5E082FG03]に分類される特許

81 - 100 / 375

誘電体素子及び誘電体素子の製造方法

【課題】高容量であり且つリーク特性が良好である誘電体素子及びその製造方法を提供する。

【解決手段】誘電体素子10は、基板12と、12基板上に積層された誘電体膜18と、を備え、誘電体膜18は、柱状結晶からなる第1の誘電体層14と第2の誘電体層16とが、基板表面に対して垂直な方向に積層されたものであり、それぞれの誘電体層に含まれる柱状結晶は、積層界面において互いに不連続である。この誘電体素子10では、柱状結晶が積層界面において不連続であるため、柱状結晶の結晶粒界におけるリーク電流の発生が抑制され、誘電体素子10のリーク特性が向上する。また、誘電体膜18に含まれる複数層の誘電体層はいずれも柱状結晶からなることから、容量の低下が抑えられる。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】簡便な手法で、従来の強誘電体薄膜よりも大幅に比誘電率を向上し得る、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Ndを含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合で、かつ、BとAとのモル比B/Aが0.005≦B/A<0.03の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】リーク電流の低減と絶縁耐圧の向上の両特性をバランスよく改善することができる、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、P(燐)を含む複合酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、複合金属酸化物Aを構成するための原料並びに複合酸化物Bを構成するための原料が上記一般式で示される金属原子比を与えるような割合で有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

圧電素子

【課題】本発明の目的は、セラミックスの結晶化温度を低減させることができ、セラミックスの表面モフォロジを改善することができる、セラミックスの製造方法を提供することにある。

【解決手段】セラミックスの製造方法は、酸素八面体構造を有する複合酸化物材料と、該複合酸化物材料に対して触媒作用を有する常誘電体材料とが混在した膜を形成し、その後該膜を熱処理することを含み、前記常誘電体材料は、構成元素中にSiを含む層状触媒物質、または構成元素中にSi及びGeを含む層状触媒物質からなる。前記熱処理は焼成及びポストアニールを含み、少なくとも該ポストアニールは、加圧された、酸素及びオゾンの少なくとも一方を含む雰囲気中で行われることが望ましい。セラミックスは、酸素八面体構造を有する複合酸化物であって、該酸素八面体構造中にSi及びGeを含む。

(もっと読む)

薄膜電子部品及び薄膜電子部品の製造方法

【課題】 薄膜電子部品の性能の低下を防ぐことの可能な薄膜電子部品及びその製造方法を提供する。

【解決手段】 本発明に係る薄膜電子部品は、基材10と、基材10の一方の主面上に形成されると共に第1の開口部14aにより第1の主要部21と第1のアイランド部20とに分離された第1の導電層14と、第1の主要部21上を覆うと共に第1の開口部14aを充填する誘電体層16と、誘電体層16の少なくとも一部を覆うと共に第1の導電層14の第1のアイランド部20と接する第2の導電層23と、第1の導電層14の第1のアイランド部20と第2の導電層23とが接触する領域において第1のアイランド部20と第2の導電層23とを貫通する第1の開口50と、基材10を貫通して第1の開口50に連通する第1の貫通孔52と、を備えている。

(もっと読む)

広帯域容量素子

【課題】低周波数帯域のキャパシタンスを小さくせず、容量性部品の使用周波数の上限を高周波帯域に広げた広帯域容量素子を提供する。

【解決手段】電極板101の上に、組成の異なる誘電体板111、112が形成され、その上に電極板102が形成される。誘電体板111、112の内少なくとも一方は、対象周波数帯域において、分極の特異点を有する。例えば、誘電体111を炭化珪素SiC、誘電体112を酸化アルミニウムAl2O3で形成し、誘電体111は、246MHzにおいて分極の特異点を有する。即ち、246MHzを境に誘電率が大きく変化する。

(もっと読む)

高密度コンデンサまたは他の顕微鏡的層を有する機械的デバイスの製造方法

非常に大きい層数を有する大容量コンデンサを生成する方法。導電および絶縁材料の相互層構造は、真空または不活性ガスチャンバを壊すことなくイオン堆積によって堆積される。平面基板のために、層堆積は、基板の両面上に、そして複数の基板上に、同時に進行してよい。連続堆積は、丸い基板のために用いられてよい。デバイスの内側層は、容量の改良のために原子近接効果を生み出すために、酸化アルミニウムのための約80〜140のオングストロームの、そしてアルミニウムのための約40〜70のオングストロームの範囲の顕微鏡的な厚みを有してよい。欠陥は、自己回復作用によって、そして、隔離アイランドの作成によって、適応されてよい。 (もっと読む)

量子ドット型ウルトラキャパシタ及び電子バッテリー

【課題】キャパシタよりもエネルギー密度を大きくし、バッテリーよりも充電/放電を速くし、かつ/またはバッテリーよりも寿命をずっと長くしたエネルギー貯蔵装置を提供する。

【解決手段】本発明は、少なくとも1つの量子閉じ込め系(QCS)を有するソリッドステート・エネルギー貯蔵装置を提供する。ここで、QCS(102)は、量子ドット(QD)、量子井戸またはナノ細線を含み得る。本発明は、少なくとも1つのQCSが組み込まれた少なくとも1つの誘電材料(104)層と、少なくとも1つの誘電材料層の上面に配置された第1導電電極(106)及び下面に配置された第2導電電極(108)とをさらに含み、両電極は、少なくとも1つのQCSに電荷を移動させるように配置されており、両電極間に電圧を与えるように電気回路が配置されたとき、該電圧により、移動した電荷が少なくとも1つのQCSから電気回路へ放電されるようにした。

(もっと読む)

誘電体薄膜素子の製造方法

【課題】金属箔の酸化を防止しながら、絶縁抵抗を充分高くできる誘電体薄膜素子の製造方法を提供する。

【解決手段】誘電体薄膜素子の製造方法は、金属箔11上に形成された誘電体薄膜12を、真空雰囲気又は還元雰囲気の下で400〜1200℃に加熱する焼成工程S3と、焼成工程S3の後に、還元雰囲気でアニール処理を行う還元アニール工程S4と、を備える。これにより、金属箔の酸化を防止しながら、リーク電流を低減でき、絶縁抵抗を充分高くできる。

(もっと読む)

キャパシタ及びその製造方法

【課題】MIMキャパシタの製造工程時においてポリマーや導電性残留物の発生を最小化し、これにより、上部電極と下部電極との間または隣り合う導電層(配線)との短絡を防止し、リーク電流を改善させることができるキャパシタ及びその製造方法を提供すること。

【解決手段】本発明は、下部電極と、前記下部電極の一部を覆うように前記下部電極上に形成された誘電体膜と、前記誘電体膜上に形成された上部電極と、前記上部電極上に形成されたハードマスクパターンと、前記ハードマスクパターン、前記上部電極、及び前記誘電体膜の側壁にスペーサ状に形成された分離膜と、を備えるキャパシタを提供する。

(もっと読む)

ナノ粒子薄膜の製造方法、ナノ粒子薄膜及びそれを用いた電子デバイス

【課題】緻密で広範囲で均一であると共に、クラックや剥離の発生しにくいナノ粒子薄膜の製造方法、ナノ粒子薄膜、及びそれを用いた電子デバイスを提供する。

【解決手段】ナノ粒子15を分散媒中に分散させ、ナノ粒子分散液11を調製する工程Aと、導電性の基材12の表面を、分散液11中におけるナノ粒子15の表面電荷と逆の電荷を有する高分子電解質の被膜14で被覆する工程Bと、高分子電解質の被膜14で被覆された基材12及び対電極13を分散液11中に浸漬し、電気泳動堆積法により高分子電解質の被膜14で被覆された基材12上にナノ粒子15を堆積させる工程Cとを有することを特徴とするナノ粒子薄膜の形成方法、この方法により製造されたナノ粒子薄膜10、及びこれを用いた電子デバイス。

(もっと読む)

構造体、キャパシタ、及びキャパシタの製造方法

【課題】簡易且つ安価な製造工程によって形成可能な大容量小型キャパシタ用の構造体、キャパシタ、及びその製造方法を提供すること。

【解決手段】 第1の下地上に形成され、第1の誘電体膜によって表面全体が覆われた複数の第1の導体粒子を含み、前記複数の第1の導体粒子が前記第1の誘電体膜によって互いに隔離された第1の誘電体層と、前記第1の誘電体層に積層され、前記第1の誘電体層より誘電体が占める体積の割合が高い第2の誘電体層とを含むこと。

(もっと読む)

フィルムコンデンサ及びその製造方法

【課題】フィルム上に金属膜が形成された金属化フィルムを捲回してなるフィルムコンデンサにおいて、基材上にコーティング組成物を塗布してフィルムを形成するコーティング法の製造コストを低減できるような構成を得る。

【解決手段】金属箔(19c)上にコーティング組成物を塗布してなる絶縁フィルム(19a)の表面上に、幅方向端部にマージン部(21)が設けられるように金属膜(19b)を形成してなる両面電極フィルム(19)と、金属化フィルム(20)とを、該両面電極フィルム(19)において上記マージン部(21)が設けられた幅方向端部で金属箔(19c)を上記引出電極(14)の一方に電気的に接続するとともに、該両面電極フィルム(19)の金属膜(19b)を上記引出電極(15)の他方に電気的に接続するように、重ね合わせて捲回する。

(もっと読む)

薄膜コンデンサ

【課題】第一配線と第二電極との間に水平方向の位置ずれが発生した場合であっても、製造における容量の精度及び安定性を向上させることが可能な薄膜コンデンサを提供する。

【解決手段】矩形状の第一電極2と、第一電極2と第二電極4との間に介装された誘電体層と、第一電極2よりも面積が大きい矩形状の第二電極4を順次積層した薄膜コンデンサ1であって、直線状の第一配線8及び対向配線10を備え、第一配線8及び対向配線10の一端を、それぞれ、薄膜コンデンサ1の平面視において、互いに対向させて第一電極2に接続し、第一配線8の幅と対向配線10の幅を同一とし、第一配線8の長さ方向と対向配線10の長さ方向を同一とし、第一配線8及び対向配線10の他端を、薄膜コンデンサ1の平面視において、第二電極4から突出させる。

(もっと読む)

電気化学電池またはキャパシタ用の3Dナノ構造電極を形成するための装置および方法

本明細書に記載される実施形態は、一般に、電気化学電池またはキャパシタ用の電極構造に関し、特に、寿命がより長く、製造コストがより低く、プロセス性能が改良された、信頼性が高く費用対効果が高い電気化学電池またはキャパシタ用の3D電極ナノ構造を製造するための装置および方法に関する。  (もっと読む)

(もっと読む)

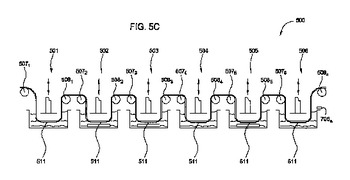

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

いわゆるクアンタム・バッテリに電気エネルギーを蓄積する新しい方法

【課題】現時点で使用可能な「スーパー・コンデンサ」は異なる物理原理で動作している。これらのスーパー・コンデンサは低電圧でしか動作せず、機械的な衝撃に敏感であり、ある高い抵抗を示し、数桁低いエネルギー密度及び出力密度を有する。

【解決手段】電気絶縁マトリックス材料又は中間層に埋め込まれ、複合箔又は固定された平らなベースに塗布されたナノメートル・サイズの粒子又は層の形態で化学的に高双極子性の結晶からなる材料から、クアンタム・バッテリ(スーパー・コンデンサ)を製造することができる方法を開示する。

(もっと読む)

チューナブル素子およびその製造方法

【課題】基板と強誘電体薄膜との格子ミスマッチによる歪みが効率的に緩和されるペロブスカイト構造強誘電体薄膜を提供すること。

【解決手段】本発明によるチューナブル素子は、基板上に(111)エピタキシャル成長したペロブスカイト構造強誘電体薄膜を含んでなる。特に、ペロブスカイト構造強誘電体薄膜は、(111)エピタキシャル成長した(BaxSr1−x)TiO3またはPb(ZrxTi1−x)O3{0<x<1}からなる。

(もっと読む)

金属酸化物層の製造方法

【課題】金属酸化物層の表面のアモルファス層を低減し、金属酸化物層の誘電率を向上させること。

【解決手段】金属酸化物の前駆体層を分解して金属酸化物層を形成する工程と、金属酸化物層にレーザを照射して前記金属酸化物層を結晶化する工程と、結晶化された金属酸化物層に対して、10〜300Hzの間隔で、最初のパルスの照射フルエンスを60〜100mJ/cm2とし、最後のパルスの照射フルエンスを10mJ/cm2以下とし、照射フルエンスの減少速度Vが−150≦V[mJ/(cm2min)]<0となるように、各パルスの照射フルエンスを減少させながらパルスレーザを照射する除冷工程と、を備える金属酸化物層の製造方法。

(もっと読む)

バルクコンデンサとその製造方法

【課題】高いキャパシタンス密度を達成可能なコンデンサとその製造方法を提供する。

【解決手段】バルクコンデンサは、金属箔から形成された第1電極と、金属箔上に形成された半導体の多孔質セラミック本体と、多孔質セラミック本体の上に例えば酸化処理により形成された誘電体層と、多孔質セラミック本体の気孔に充填されて第2電極を形成する導電性媒質を有する。コンデンサには、カプセル化用の各種の層や電気的終端を形成してもよい。バルクコンデンサの製造方法では、金属箔から形成された第1電極の上に半導体の多孔質セラミック本体を形成し、酸化処理して誘電体層を形成し、多孔質セラミック本体に導電性媒質を充填して第2電極を形成する。金属箔と多孔質セラミック本体の間に半導体のセラミック薄膜層を形成してもよい。

(もっと読む)

81 - 100 / 375

[ Back to top ]