Fターム[5F033XX00]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696)

Fターム[5F033XX00]の下位に属するFターム

平坦化 (793)

段差被覆性改善、段切れ防止 (570)

微細化 (1,181)

エレクトロマイグレーション防止 (477)

ストレスマイグレーション防止 (204)

オーミック性向上 (46)

低抵抗化 (1,713)

低融点化 (3)

密着性改善 (1,147)

エッチングマスクのずれ対策 (331)

ヒロック防止 (130)

クラック防止、歪み防止 (509)

腐食防止 (505)

応力の利用、応力の低減 (758)

酸化防止 (315)

残さの除去 (252)

放熱 (140)

基板と配線又は配線間の干渉防止 (1,198)

信号の遅延防止、伝達の同時化 (255)

拡散、突き抜け防止 (992)

短絡防止 (613)

遮光 (95)

製造工程の簡略化 (781)

製造コストの低下 (762)

成膜時の膜厚の制御 (46)

配線修理 (121)

検査、試験 (367)

Fターム[5F033XX00]に分類される特許

1,381 - 1,392 / 1,392

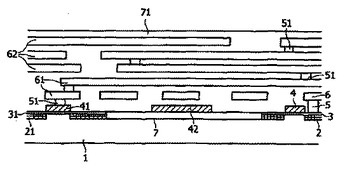

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

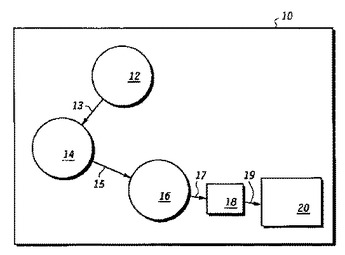

半導体製造プロセスの過程で導電面を不動態化するための方法

半導体ウェハの製造プロセスが開示されている。メタル配線の表面に発生するデンドライトや電気分解反応を抑止するため、半導体ウェハに対して溶液が適用される。その溶液は、CMP処理の際又はCMP洗浄後処理の際に適用される。その溶液は、界面活性剤及び防食剤を含む。一実施形態では、その溶液中に含まれる界面活性剤の濃度が約1重量パーセント未満に設定され、防食剤の濃度が約1重量パーセント未満に設定される。また、その溶液は、溶媒及び共溶媒を含むこともできる。別の実施形態では、その溶液が、界面活性剤及び防食剤を含まず、溶媒及び共溶媒を含む。一実施形態では、CMP処理及びCMP洗浄後処理を、約1μm未満の波長を持つ光の存在下で実施できる。  (もっと読む)

(もっと読む)

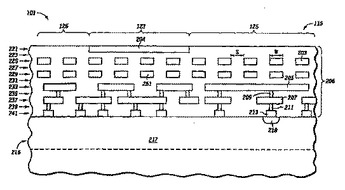

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

多層配線構造を備えた半導体装置

【課題】本発明の課題は、多層構造の配線層に加わるパッケージの熱収縮による応力を効果的に緩和し、チップの保護膜であるパッシベーション膜のクラックの発生などを防止できる半導体装置を提供することである。

【解決手段】上記課題は、半導体基板11上に層間絶縁膜14を介して下層配線と13上層配線15とが形成される多層配線構造を備えた半導体装置において、層間絶縁膜14の面積が広くとれるように該層間絶縁膜14に開ける開口を小さくすることを特徴とする多層配線構造を備えた半導体装置にて解決される。

(もっと読む)

半導体装置およびその製造方法

【課題】 ポストの配置や形状を変えることなくチップの向きを一目瞭然にすることができる半導体装置およびその製造方法を実現する。

【解決手段】 ダイシングにより個片化された時に、チップの一辺側面に切削残留して露出する識別ポスト20を設けたので、従来のように、ポスト6の配置や形状を変えることなく、チップの向きが一目瞭然になる。また、チップの向きを表すマークとなる識別ポスト20は、チップの一辺側面に露出される為、チップを傾ければ、チップの表面側や裏面側からでもチップの向きを識別でき、ハンドリング性が向上する。

(もっと読む)

多層配線基板及び半導体装置

【課題】エミッタ配線からバイアホール、サーマルビアを介して多層配線基板下面につながる放熱経路の熱抵抗を低減し、半導体装置全体の熱抵抗を低減すること。

【解決手段】厚さ方向に貫通孔4を有する多層配線基板3において、多層配線基板3に実装される半導体基板1がその厚さ方向に貫通孔5を有し、かつ、多層配線基板3及び半導体基板1の厚さ方向と直交する平面内において、半導体基板の貫通孔5の占める領域全体が多層配線基板内貫通孔4の占める領域に含まれている多層配線基板。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

金属配線構造及びその製造方法

【課題】オーバーエッチングが十分に行えて、しかもアルミニウム配線層の片落ちを起こすことのない微細ピッチの金属配線構造及びその製造方法を提供する。

【解決手段】バリアメタル層11、実質的なアルミニウム配線層12、さらに破線で示すフォトレジスト層PRと接触する、最上層がタングステン膜(W)で構成されるキャップ層13が順に積層されている。このような配線パターンのエッチングに際し、オーバーエッチングによりフォトレジスト層PRが目減りしてエッジ部分が型崩れすることがあっても、アルミニウム配線層12の形状には影響ない。すなわち、最上層のタングステン膜(W)は、アルミニウム配線層12をエッチングする際のエッチングマスク(ハードマスク)となり得るからである。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

1,381 - 1,392 / 1,392

[ Back to top ]