Fターム[5F044KK17]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984) | 形状、配置 (280)

Fターム[5F044KK17]に分類される特許

41 - 60 / 280

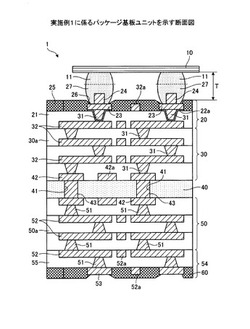

パッケージ基板ユニット及びパッケージ基板ユニットの製造方法

【課題】半導体チップの半田バンプとパッケージ基板ユニットの半田バンプとの接続信頼性の向上及び半田バンプ間での狭ピッチ化を図れるパッケージ基板ユニット及びパッケージ基板ユニットの製造方法を提供する。

【解決手段】パッケージ基板ユニット1の半導体チップ実装層20は、絶縁層21と、絶縁層21の上面に形成された導電めっきシート層22aと、導電めっきシート層22aの上面に形成された導電パッド23と、導電パッド23の上面のほぼ中央部に形成される金属ポスト24と、導電パッド23及び金属ポスト24とを包囲するように形成されたソルダーレジスト層25とを備える。

(もっと読む)

電子機器

【課題】 ICチップをCOG実装する際に、ACF熱圧着時のACF流動による流動圧力を均一にし、実装の信頼性を向上させる。

【解決手段】 ICチップ1の出力バンプの配列において、ACF流動の流動圧力が均等にかかるように、右上がりに千鳥配列されたバンプ群12と左上がりに千鳥配列されたバンプ群11を形成し、ICチップ1上に左右均等に配置する。

(もっと読む)

位置あわせ方法、接合構造、半導体装置、及び半導体装置の製造方法

【課題】簡易な構成で精度よく微細な接合対象物同士を位置あわせができる構造体を提供する。

【解決手段】第1の接合部1を有する第1の接合対象物の所定の箇所に開口12を形成する。第2の接合部2を有する第2の接合対象物の前記開口12と対向する位置に、前記開口12の径よりも小さい径を有し加熱により体積膨張する性質を有する球状構造体3を配置する。前記球状構造体3が前記開口12内に位置するように、前記第1の接合対象物と前記第2の接合対象物を仮配置する。加熱により、前記球状構造体3を前記開口12内で前記開口12の径の大きさまで体積膨張させることによって、前記第1の接合部1と前記第2の接合部2とを自己整合的に位置あわせする。

(もっと読む)

導電接合構造、実装構造体及び導電接合方法

【課題】より多くの導電粒子を電極間に捕捉可能な導電接合構造と、導電接合構造によって実装基板に実装部品を接合した実装構造体、及び、この導電接合構造によって2つの被接合部材を接合するための導電接合方法を得る。

【解決手段】基板側電極18には接合用凹部24が形成され、部品側電極20には接合用凸部26が形成される。接合用凹部24と、接合用凸部26の間に、異方性導電接合材22の導電粒子22Pを捕捉する捕捉間隙30が構成されている。

(もっと読む)

配線基板

【課題】

熱容量の異なる半導体素子接続パッドに半田バンプを介して半導体素子の電極を接続する際、半田バンプ同士の短絡を防ぎ半導体素子の正常作動が可能な配線基板を提供すること。

【解決手段】

ビア導体2aが充填された多数のビアホール1cを有する絶縁層1bの表面にビア導体2aと一体的に形成された導体層2から成る第1の半導体素子接続パッド3aと、絶縁層1b上に形成された導体層2のみから成る第2の半導体素子接続パッド3bとが、第1の半導体素子接続パッド3aの配列中に第2の半導体素子接続パッド3bが分散して配設されるとともに第1および第2の半導体素子接続パッド3aおよび3bに半田バンプ5が溶着されて成る配線基板10であって、第2の半導体素子接続パッド3bに溶着された半田バンプ5の体積が第1の半導体素子接続パッド3aに溶着された半田バンプ5の体積より小さい配線基板10である。

(もっと読む)

ドライバ

【課題】ドライバの半導体集積回路装置の出力端子数が増加しても、半導体集積回路装置内部の配線層による電圧降下を防止する。

【解決手段】第1の配線層と第2の配線層とが形成されたフィルム基板と、前記フィルム基板上にチップオンフィルム方式で実装された半導体チップとを有し、前記第1の配線層と前記半導体チップの出力端子とが電気的に接続され、前記第2の配線層によって、前記半導体チップの複数の端子同士が電気的に接続されており、前記第2の配線層を介して、前記半導体チップの電源、或いはクロックが伝達される。前記第2の配線層は、前記半導体チップと前記フィルム基板との間に形成される。

(もっと読む)

半導体装置

【課題】導電部材のバリを有さない半導体装置を提供する。

【解決手段】配線基板2と、機能素子4が形成された機能面3aを有し、この機能面3aを配線基板2の一方表面に対向させて、この一方表面との間に所定間隔を保持して接合されかつ電気的に接続された半導体チップ3と、配線基板2の一方表面上に形成され、配線基板2の端面2eとほぼ面一の端面を有する導電膜6と、配線基板2と半導体チップ3との間および導電膜6上に形成された封止樹脂層7とを含み、半導体チップ3において、機能面3aと反対側の面は露出している半導体装置。

(もっと読む)

電子装置

【課題】

本発明は、集積回路素子の電極パッドと、金バンプと半田で形成されたボールとの接合強度の低下のない電子装置を提供することを課題とする。

【解決手段】

本発明の電子装置は、集積回路素子と、集積回路素子の回路の形成された面の電極パッド上に固着される金バンプと、金バンプを包む半田と、集積回路素子の電極パッドが金バンプと半田を介して接合される素子搭載部材と、素子搭載部材に配置された集積回路素子搭載用パターンとを備え、半田の体積に対する金バンプの体積比率を12パーセント以上16パーセント以下とした。

(もっと読む)

部分パット上にバンプを有するフリップチップ相互接続構造を形成する半導体デバイスおよびその方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、露出側壁を有し、SRO+2*SRR−2Xによって定義される設計規則に従ってサイズ決定される相互接続部位を伴って、前記基板上に複数の伝導性トレースを形成するステップであって、式中、SROは、前記相互接続部位上の開口部であり、SRRは、製造工程のための位置合わせであり、Xは、接触パッドの前記露出側壁の厚さの関数である、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

電子部品、電子機器及びそれらの製造方法

【課題】先アンダーフィル方式のフリップチップボンディングにおいて、接続不良が少ない電子部品を提供する。

【解決手段】電子部品20の基板21上に形成されたフリップチップボンディング用の突起電極24の上面に形成された窪み26と、窪み26に埋め込まれたフラックス25と、突起電極24の外側の基板21上に形成され、突起電極24を突起電極24上面まで埋め込む接着材22とを有する。ボンディングの際にフラックスが蒸発して接合面の気圧が上昇し、溶融した接合樹脂の接合面への侵入が防止される。このため、接合面に絶縁性接着材の皮膜が形成されず接続不良を生じない。

(もっと読む)

半導体装置の構造および製造方法

【課題】挟ピッチかつ高い接続信頼性を確保した簡易な構造の半導体装置、および製造方法を提供する。

【解決手段】半導体素子1の電極端子1b上に突起状電極1aを形成する。突起状電極1aよりも大きくし、位置を合わせた転写用の金型4に、粘着層5を供給し半田粒子3を付与する。金型4と半導体素子1の対向する位置を合わせ、加熱・加圧して半田粒子3を突起状電極1a上に付与、金型4を引き剥がして半導体素子1を個片化する。半導体素子1の突起状電極1aに対向して回路基板2の電極端子2aの位置を合わせて、加熱、荷重し半導体素子1を回路基板2上へ搭載する。半導体素子1の端部の回路基板2との距離が最も大きな電極同士でも、微細半田が鼓状に伸びて接合し平行度の悪化を吸収する。端部電極の熱応力集中を微小半田接合体(半田接合部3c)が受けて、電極直下の脆弱な絶縁膜の熱応力を低減して剥離や亀裂を防ぎ、高い接続信頼性を確保する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体装置31は、回路基板1の所定位置に形成された電極パッド10を有し、電極パッド10には、半導体装置21のハンダバンプ26が接合されている。ハンダバンプ26は、半導体装置21の電極25上に形成され、そのハンダ材料には鉛フリーハンダが用いられている。回路基板1の電極パッド10は、複数の凸部10Aと溝10Bが形成されており、ハンダバンプ26は、その一部が電極パッド10の溝10Bを埋めるように入り込んでいる。

(もっと読む)

半導体デバイスの実装方法

【課題】半導体デバイスを積層化した構造で、低背化が可能な手段を提供する。

【解決手段】半導体デバイス10の導電体12に複数の微小な金属塊13を形成、樹脂よりもヤング率が大きい半導体インターポーザ15の導電体17に複数の微小な金属塊18を形成しフリップチップ接続することで、導電体同士が微少な金属塊で接続されることになり低背化が達成された。また、積層化プロセスが容易になるように、前記金属塊の形状、大きさ、配置などを最適化した。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体パッケージにおいて長期接続信頼性を向上させ、エレクトロマイグレーション耐性を改善する。

【解決手段】半導体素子1の電極パッドと基板21上の電極パッド20とをはんだボールによって接続する。はんだボールは、金属製コア部11と、金属製コア部11の周囲に設けられ、前記コア部11よりも剛性が低く融点が低いはんだ部10とで構成されている。はんだボールを半導体素子1にリフローによって接続する。その後、半田ボールが付いた半導体素子1と基板21を超音波にて接続し、基板21側において、金属コア11と電極20を直接接続する。これによって熱ストレスの少ない、かつ、抵抗の小さい接続を可能とする。

(もっと読む)

電子装置およびその製造方法

【課題】小さな圧力を用い電極同士を接合可能とすること。

【解決手段】規則性を有し配列した複数の突起14を備えた第1電極12を含む第1基体10と、前記複数の突起14とそれぞれ嵌合した複数の嵌合部26を備え、前記第1電極12と機械的かつ電気的に接続された第2電極22を含む第2基体20と、を具備する電子装置。

(もっと読む)

半導体デバイス実装体とその製造方法

【課題】半導体デバイスを基板に実装した後に熱負荷が加えられても位置ずれが生じない半導体デバイス実装体を提供する。

【解決手段】基板2には3つの電極4a,4b,4cが設けられており、光半導体素子3には、基板2の電極4a,4b,4cと対向する位置に電極5a,5b,5cが設けられている。シリコン基板2の電極4a,4bと光半導体素子3の電極5a,5bは金製のスタッドバンプ7によって接合されており、シリコン基板2の電極4cと光半導体素子3の電極5cは、半田6によって接合されている。スタッドバンプ7は予めシリコン基板2の電極4a,4bに設けられていたものであり、このスタッドバンプ7の先部が、光半導体素子3の金メッキされた電極5a,5bに固相接合されている。

(もっと読む)

電極、電子部品及び基板

【課題】電極本体と電子部品又は基板との接合面積の低下を抑制できる電極、電子部品及び基板の提供を課題とする。

【解決手段】本発明は、電子部品12にはんだ付けされて設けられ、電子部品12が基板13に実装される際に、基板12にはんだ付けされる電極10である。この電極10は、電子部品12及び基板12にはんだ付けされる柱状の電極本体11を有している。電極本体11が電子部品12又は基板13にはんだ付けされる際に、電極本体11の接合面11a,11bと電子部品12又は基板13との間におけるはんだ14内に発生する空気溜まり15内の空気15aを排出する空気排出手段としての溝20を備えている。

(もっと読む)

3次元でパッケージされた集積回路に対するダイ間結合の間の静電放電ダメージへの感受性の低減

本発明は、電子集積回路パッケージの製作、より具体的には3次元でパッケージされた集積回路を製造する際の静電放電ダメージの軽減に関する。一実施形態では、第2層ダイが第1層ダイと接触して配置されるとき、第2層ダイおよび第1層ダイ上の他の信号導電バンプおよびパワー導電バンプが電気的に接触する前に、第2層の基板と電気的に結合された第2層の周辺部付近の導電バンプが、第1層の基板と電気的に結合された第1層の対応する導電バンプと接触する。  (もっと読む)

(もっと読む)

電子部品の実装接続構造

【課題】複数の半導体素子を有する半導体装置と樹脂基板をバンプ接続する際、半導体素子のバンプに対する熱応力の作用によって接続部にクラックが生じて、機器の長期信頼性が低くなること。

【解決手段】複数の半導体素子を搭載されるインターポーザー配線基板の裏面に複数のランドとバンプを備える半導体装置と、複数のランドが配列された樹脂基板とを接続する電子部品の実装構造であって、前記インターポーザー配線基板の前記半導体素子と重なる位置にあるバンプの中で、半導体装置の中心から最も離れた位置に配列された位置及びその周辺にあるバンプと、前記バンプと隣接するバンプとが並列接続されていることを特徴とすることにより、応力集中が最も発生する位置のバンプが、冗長接続となり、一つのバンプが破断しても他方のバンプの接続が保たれ、故障を起こす期間を延伸することができる。

(もっと読む)

多様な集積回路チップバンプピッチを有する半導体装置

チップ回路への電気的接続を可能にする複数のボンディングパッドを含む集積回路基板を含む半導体装置が記載される。ボンディングパッドは、予め製造された孔を有するパッシベーション層によって少なくとも部分的に覆われる。装置は、ボンディングパッド上部に複数のバンプを有するチップを含み、バンプの領域はパッシベーション層の協働する孔の各々の領域と比較して大きい。  (もっと読む)

(もっと読む)

41 - 60 / 280

[ Back to top ]