Fターム[5F044KK17]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984) | 形状、配置 (280)

Fターム[5F044KK17]に分類される特許

21 - 40 / 280

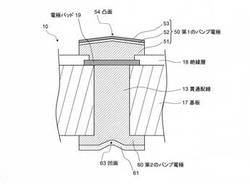

半導体チップ、半導体装置および半導体装置の製造方法

【課題】バンプ電極同士の横滑りを防止し、バンプ電極同士を接合する接合材料のはみ出しを抑制する。

【解決手段】

半導体チップ10は、基板17と、基板17の一方の面に設けられた第1のバンプ電極50と、基板17の他方の面に設けられた第2のバンプ電極60と、第1のバンプ電極50と第2のバンプ電極60のうちの少なくとも一方の頂面に形成された導電性の接合材料層61と、を有している。第1のバンプ電極50の頂面は凸面54であり、第2のバンプ電極60の頂面は凹面63である。

(もっと読む)

電子装置及びその製造方法

【課題】 信頼性の高い電子装置を提供すること。

【解決手段】 外表面に電極31を有する電子部品3と、基板本体21、および基板本体21の一方主面に設けられ電子部品3の電極31と電気的に接続された電気配線22を含む配線基板2とを備え、基板本体21の表面と、電子部品3の下面とは、直接接合している電子装置1である。電子部品3と配線基板2との間には別体の部材が存在しない。よって、異なる部材同士の境界が減少するので、剥離の可能性を低減できる。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

配線基板及びその製造方法

【課題】本発明は、表面に配列された端子パッドの半田接合力を向上させる配線基板及びその製造方法を提供することを目的とする。

【解決手段】表面に半田接合用の複数の端子パッド20〜24、27、28を有する配線基板10、10a〜10gであって、

前記複数の端子パッドは、平面形状が正多角形に形成され、

該正多角形の内心Iが、所定のピッチLで配列されたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法並びに電子装置

【課題】バンプ接合の界面における剥離を抑制すること。

【解決手段】第1バンプ32が形成された素子10と、第2バンプ34が形成され、前記素子とは熱膨張係数の異なる基板20と、を具備し、前記第1バンプの終端面33は、前記素子の内側に向かって傾斜して形成され、前記第2バンプの終端面35は、前記第1バンプの終端面に対応するように形成され、前記第1バンプの終端面と前記第2バンプの終端面とが接合されている半導体装置。

(もっと読む)

半導体装置

【課題】第1の半導体集積回路と第2の半導体集積回路とをフリップチップ工法で1つの基板上に搭載して半導体装置とする場合に、第1の半導体集積回路のパッド列を複数段としながら、第1の半導体集積回路から第2の半導体集積回路への配線をビアを介さずに行い得るようにする。

【解決手段】第1の半導体集積回路32と第2の半導体集積回路33とが基板31上に配置される。前記第1の半導体集積回路32には、その辺方向に延びる外側パッド列34Rが備えられる。また、前記第1の半導体集積回路32の外側パッド列34Rの内方には、前記外側パッド列34Rと並行に延びる内側パッド列35が備えられる。前記外側パッド列34Rのうち、前記内側パッド列35に対向する部分のパッド列34Raは、前記基板31に配置された金属配線36により、前記第2の半導体集積回路33の各パッド33aに電気的に接続される。

(もっと読む)

電子部品及び電子部品の製造方法

【課題】半導体装置及び配線基板の接続信頼性がより向上した電子部品等を提供する。

【解決手段】本発明に係る電子部品は、第1基板と、前記第1基板の第1の面に位置する電極と、前記第1基板の前記第1の面に形成される第1樹脂突起と、前記第1基板の前記第1の面に形成される第2樹脂突起と、前記電極と接続し、前記第1樹脂突起の少なくとも一部を覆う第1の部分と、前記第2樹脂突起の少なくとも一部を覆う第2の部分と、を有する第1配線と、第2基板と、前記第2基板の第2の面に位置する第2配線と、前記第2基板の前記第2配線と接する突起電極であって、前記第1の部分および前記第2の部分と接する前記突起電極と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

基板の接続構造、基板セット、光センサアレイ装置及び基板を接続する方法

【課題】基板と基板との突き合わせ接続時に、2つの基板の間の相対的な位置がずれていても、2つの基板が電気的に接続される基板の接続構造を提供する。

【解決手段】本明細書に開示する基板の接続構造は、複数の第1電極15が配置された第1電極面12を有する第1基板11と、複数の第2電極16が配置された第2電極面14を有し、第2電極面14が第1電極面12と対向する第2基板13と、を備え、複数の第2電極16それぞれは、第2電極面14の中心C2を除いて、第1電極15と対向する第2電極面14上の位置に対して、第2電極面の中心C2とは反対の方向にずれて配置されており、複数の第2電極16それぞれは、対向する第1電極15とバンプ17を介して電気的に接続している。

(もっと読む)

配線基板およびはんだバンプ付き配線基板ならびに半導体装置

【課題】 絶縁基板に配置された接続パッドに半導体素子の電極がはんだバンプを介して接合される配線基板において、接続パッドのエレクトロマイグレーションによる空隙が抑制された配線基板を提供する。

【解決手段】 上面に半導体素子の搭載部1aを有する絶縁基板1と、搭載部1aに配置された、半導体素子4の主面の電極5がはんだバンプ6を介して接合される接続パッド2と、絶縁基板1の搭載部1aから内部にかけて形成され、端部が接続パッド2に接続された貫通導体3とを備え、接続パッド2の上面に、平面視で貫通導体3の端部が接続された領域の外側に、はんだバンプ6よりも電気抵抗が低い金属材料からなる凸部2aが形成されている配線基板である。貫通導体3からの電流を凸部2aに分散させて接続パッド2における電流密度を低く抑え、エレクトロマイグレーションによる空隙を抑制できる。

(もっと読む)

扁平はんだグリッド配列のための処理方法、装置及びコンピュータシステム

【課題】プリント回路基板表面実装部品のための扁平はんだグリッド配列を提供する。

【解決手段】スタンドオフ接触配列は、フリップフロップパッケージの実装基板とボードとの間に配置される(410)。このスタンドオフ接触配列は、実装基板上の扁平なはんだバンプをボード上の扁平なはんだペーストと結合する(430)ことによって、形成可能である。その後に、スタンドオフ接触配列は、実装基板上の扁平なはんだバンプに対してボード上の扁平なはんだペーストをリフローする(440)ことによって、形成される。

(もっと読む)

半導体装置

【課題】アンダーフィル樹脂の充填が困難な場合であっても、半導体装置の信頼性が低下することを防ぐ技術を提供する。

【解決手段】半導体チップ(2)と、基板(8)と、チップ面に形成されたチップ面絶縁層(7)と、基板面に形成された基板面絶縁層(10)と、フリップチップボンディングによってチップ側電極(4)と基板側電極(9)とを接続する接続部材(11)とを具備する半導体装置(1)を構成する。接続部材(11)は、チップ面絶縁層(7)を貫通するバンプ部分(12)と、基板面絶縁層(10)を貫通する低融点部分(13)と、バンプ部分(12)と低融点部分(13)とが接触している接触領域(16)とを備えることが好ましい。ここで、チップ面絶縁層(7)と基板面絶縁層(10)とは、空隙(14)を介して向かい合うように配置されている。そして、接触領域(16)は、空隙(14)によって露出される表面を有する。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置及びその製造方法並びに電子装置

【課題】はんだバンプを用いてFPCに実装される半導体装置において、FPCの可動部や屈曲された部分に実装することを可能にする。

【解決手段】一面に複数の電極4を配してなる半導体基板2と、半導体基板2の一面2aを覆うように配され、かつ複数の電極4が露呈するように複数の開口部3bを有する絶縁層3と、一端部が複数の電極4と電気的に接続された再配線層5と、再配線層5と電気的に接続された複数のパッド6と、複数のパッド6の一面に載置された複数のはんだバンプ7と、を備え、複数のパッド6を載置する絶縁層の一面3aが、半導体基板2の一面に平行な任意の方向から見た断面が凹円弧状になるように形成されていることを特徴とする半導体装置を提供する。

(もっと読む)

半導体素子およびフリップチップ相互接続構造を形成する方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの能動表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、前記相互接続部位よりも幅広い、ステップと、前記接続部位から離れた前記基板の領域上にマスキング層を形成するステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップと、を含む、半導体素子を作製する方法。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のフリップチップ接続における接続信頼性の向上を図る。

【解決手段】フリップチップ接続する前に基板上のフリップチップ接続用のはんだバンプ5aにフラックス9を塗布し、さらにリフロー/洗浄してからフリップチップ接続を行うことで、はんだバンプ5aの表面の酸化膜を薄くするとともに、前記酸化膜の均一化を図ることができ、これにより、フリップチップ接続時に局所的なはんだはみ出しの発生を抑制してはんだブリッジの発生を低減し、半導体装置のフリップチップ接続における接続信頼性の向上を図る。

(もっと読む)

半導体ウエハ、半導体素子、受光素子、フリップチップ接続構造、検出装置、およびこれらの製造方法

【課題】高密度のフリップチップ接合方式に用いて、実質的な面積の増大なしにバンプ同士の短絡を生じにくいバンプ配列を備える、半導体素子等を提供する。

【解決手段】バンプ9辺長Rの正方格子状に配列された電極11とを備え、正方格子を4つまとめた拡張正方格子において、コーナーではバンプは電極に合わせており、拡張正方格子の向かい合う第1組の2辺では中央のバンプは、該辺から直交方向にa(>0)だけずれ、また他の第2組の2辺では中央のバンプは、該辺から直交方向にb(>0)だけずれ、拡張正方格子の中心に位置するバンプは、上記のずれaとずれbとの合成分だけずれ、R、aおよびbは、{(a/R)−1}2+{(b/R)−1}2>1・・・・(1)、を満たしていることを特徴とする。

(もっと読む)

電子装置、回路基板、及び電子装置の製造方法

【課題】回路基板の電極パッドを拡幅化することなく、電子部品の端子を回路基板の電極パッドに確実に実装する半導体装置の製造方法を提供する。

【解決手段】電子部品の第1の端子120aにより加圧された際に前記第1の端子に対して回路基板200の実装表面と平行な第1の抗力F1aを作用させる、前記回路基板上に形成された第1の電極223aに、前記第1の端子を接触させると共に、前記電子部品の第2の端子120bにより加圧された際に前記第2の端子に対して前記第1の抗力を相殺する第2の抗力F1bを作用させる、前記回路基板上に形成された第2の電極223bに、前記第2の端子を接触させる工程と、前記第1の端子及び前記第2の端子を前記第1の電極及び前記第2の電極に加圧する工程と、を備える電子装置の製造方法。

(もっと読む)

複層銅ボンディングワイヤの接合構造

【課題】材料費が安価で、低ループ化、ボール接合性に優れ、積層チップ接続の量産適用性にも優れた、複層銅ボンディングワイヤのボール接合部の接合構造を提供する。

【解決手段】銅を主成分とする芯材21と、前記芯材の上にPd、Au、Ag、Ptのうち少なくとも1種から選ばれる貴金属を主成分とする外層22とを有する複層銅ボンディングワイヤの先端に形成したボール部を接続してボール接合部3の接合構造を形成する。前記貴金属の第1濃化部10を、前記ボール接合部の表面領域のなかでも前記銅ボンディングワイヤとの境界に位置するボール根元域9に形成する。

(もっと読む)

半導体パッケージ基板

【課題】半導体素子接続用の長手形状の接続端子の一部に凸形状を設けることにより、高密度化にも対応可能で、かつ接続に必要なボリュームと高さを有するはんだバンプを、接続端子の長手方向の所定の位置に形成可能な半導体パッケージ基板を提供する。

【解決手段】半導体素子接続用の長手形状の複数の接続端子を有し、これらの複数の接続端子が短手方向に並んで配置され、前記前記複数の接続端子の長手方向の一部に凸形状が形成されることを特徴とする半導体パッケージ基板。また、上記において、凸形状が、短手方向に並んで形成される複数の接続端子の長手方向の所定の位置に形成されることを特徴とする半導体パッケージ基板。また、上記の何れかにおいて、接続端子の長手方向における凸形状の長さが、接続端子の長さの1/5〜1/3の大きさであることを特徴とする半導体パッケージ基板。

(もっと読む)

21 - 40 / 280

[ Back to top ]