Fターム[5F058BA01]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 高耐圧 (243)

Fターム[5F058BA01]に分類される特許

41 - 60 / 243

半導体装置及びその製造方法

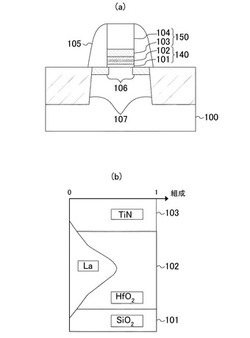

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

半導体装置の製造方法および酸化処理装置

【課題】酸化膜の形成にともなう基板へのダメージに起因した性能劣化を抑制することができる半導体装置の製造方法および酸化処理装置を提供する。

【解決手段】一の面を有する基板6aが準備される。一の面の上において酸化処理が行なわれる。酸化処理が行なわれる際、導入されたO3ガスの低温熱分解によってO(3P)ラジカルが発生させられ、該O(3P)ラジカルに光源4aが発する赤橙色光を照射し励起することによってO(1D)ラジカルが発生させられる。このO(1D)ラジカルによって基板6aの一の面の上に低温でダメージなく酸化膜が形成される。

(もっと読む)

選択的窒素化の方法

ここに、半導体装置の形成方法が提供された。ある実施の形態において、半導体装置の形成方法は、酸化物表面とシリコン表面とを有する基板を用意し、酸化物表面およびシリコン表面の双方の露出面に窒素含有層を形成し、酸化物表面上から窒素含有層を選択的に除去することによって窒素含有層を酸化する工程を有する。別の実施の形態において、シリコン特徴部上に形成された窒素含有層の残余部分上に酸化物層が形成される。また、ある実施の形態において、酸化物表面が半導体装置の1つまたはそれ以上のフローティングゲートに隣接して配置されている浅いトレンチ分離領域(STI)の露出した表面である。ある実施の形態において、シリコン表面は、半導体装置のシリコンまたはポリシリコンのフローティングゲートの露出面である。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極が微細化されても電流コラプスを抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】表面保護膜10を形成する際に、化合物半導体積層構造上に第1の絶縁膜10aを形成し、第1の絶縁膜10aの表面に、酸素原子又は窒素原子の少なくとも一方を第1の絶縁膜10aよりも多く含む第2の絶縁膜10bを形成し、第2の絶縁膜10bの上方に、第1の絶縁膜10aよりもSi−H結合を少なく含み、第1の絶縁膜10aよりも高い絶縁性を示す第3の絶縁膜10cを形成する。

(もっと読む)

High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体

【課題】High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体を提供する。

【解決手段】デバイスを形成する方法は、基板を用意するステップと、基板上に界面層を形成するステップと、界面層上にHigh−k誘電体層を堆積するステップと、High−k誘電体層上に酸素除去層を堆積するステップと、アニールを実施するステップとを含む。High−k金属ゲート・トランジスタは、基板と、基板上の界面層と、界面層上のHigh−k誘電体層と、High−k誘電体層上の酸素除去層とを含む。

(もっと読む)

強誘電体、圧電体及びこれらの製造方法

【課題】強誘電特性及び圧電特性の劣化が抑制され、リーク特性が改善された強誘電体及び圧電体を提供する。

【解決手段】BiFeO3を主成分とする強誘電体及び圧電体13は、BiFeO3の複数のFeサイトが、Tiと、Mn、Ni及びCuのいずれかとに元素置換されている。BiとFeとTiとMn、Ni及びCuのいずれかとからなるターゲットにパルスレーザを照射することで、基板11上に、BiとFeとTiとMn、Ni及びCuのいずれかとを堆積させることにより、BiFeO3を主成分とする強誘電体又は圧電体13の製造方法。

(もっと読む)

半導体素子の製造方法

【課題】欠陥が低減され膜質が良好なゲート酸化膜を有する半導体素子を製造する。

【解決手段】基板2のフィールド領域の表面にフィールド酸化膜4を形成する工程と、フィールド酸化膜4を形成した基板2の第1アクティブ領域および第2アクティブ領域の表面に第1ゲート酸化膜11A,11Bを形成する工程と、第1ゲート酸化膜11A,11Bに第1純水ヒーリングを施す工程と、第2アクティブ領域における第1ゲート酸化膜11Bを除去する工程と、第1アクティブ領域および第2アクティブ領域の表面に第2ゲート酸化膜12A,12Bを形成する工程と、第2ゲート酸化膜12A,12Bに第2純水ヒーリングを施す工程と、第1アクティブ領域および第2アクティブ領域における第2ゲート酸化膜12A,12B上にゲート電極8を形成する工程と、をこの順に有する半導体素子の製造方法。

(もっと読む)

絶縁膜形成方法、及び該方法により得られた酸化膜をゲート絶縁膜として用いる半導体装置

【課題】チャネル部分へのC原子の偏積と酸化膜内へのC原子の蓄積を独立に制御かつ低減する。

【解決手段】半導体基板の表面を熱酸化して、薄い熱酸化膜を成長させ、所望の二酸化ケイ素SiO2絶縁膜厚=前記熱酸化膜の膜厚+堆積したシリコン膜厚の100/44倍、の関係になるようにして求めた膜厚のシリコンを、熱酸化膜の上に堆積する。この堆積したシリコンを熱酸化することにより、所望の膜厚の二酸化ケイ素SiO2絶縁膜を得る。この二酸化ケイ素SiO2絶縁膜の上に、ゲート電極をデポジションしてパターニングし、かつ、ソースドレイン形成をする。

(もっと読む)

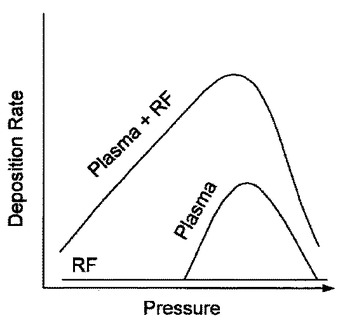

プラズマ処理方法

プラズマ反応処理を用いたフルオロカーボン層の形成方法は、マイクロ波出力及びRFバイアスを印加する工程を有する。前記マイクロ波出力及びRFバイアスは、20mTorr〜60mTorrの範囲の圧力下で印加される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率でありかつリーク電流を低減することが可能なゲート絶縁膜を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜23と、第1の誘電体膜23上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜24と、第2の誘電体膜24上に設けられた電極14とを含む。

(もっと読む)

半導体装置の製造方法

【課題】簡易に、動作中におけるON抵抗の経時変化を低減する半導体装置の製造方法を提供すること。

【解決手段】例えば、第2絶縁膜(層間絶縁膜30)が形成された半導体基板10をアニール炉に入れ600℃以上のアニール処理を施した後、酸素ガスが含まれるガス雰囲気下で前記半導体基板を前記アニール炉から取り出す半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

キャパシタ用絶縁膜、キャパシタ及び半導体装置

【課題】高い誘電率を示すキャパシタ用絶縁膜は、キャパシタに用いられた際にリーク電流が増大する。

【解決手段】2つの電極の間に挟まれて用いられるキャパシタ用絶縁膜を、チタン酸ストロンチウム又はチタン酸バリウムストロンチウムのチタンサイトの一部がハフニウム元素で置換された結晶から形成する。

(もっと読む)

半導体装置

【課題】半導体装置の特性の安定化を図ることができるとともに、半導体装置の耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置2の活性領域Aでは、半導体層4の上側の少なくとも一部に第1絶縁層18が形成されている。第1絶縁層18は、半導体層4が有するダングリングボンドを終端させる終端材料を含んでいる。耐圧領域Bでは、半導体層4の上側に第1絶縁層と異なる材料からなる第2絶縁層20が形成されており、第1絶縁層18は形成されていない。そして、第2絶縁層20が第1絶縁層18より絶縁度が高くされている。

(もっと読む)

ポリシロキサン系トレンチ埋め込み用反応物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適な溶液のポットライフが長く、トレンチへの埋め込み性が高く、HF耐性、クラック耐性を有するトレンチ埋め込み用反応物を提供する。

【解決手段】トレンチ埋め込み用縮合反応物を、該縮合反応物が少なくともポリシロキサン化合物とシリカ粒子との縮合反応物を含み、該ポリシロキサン化合物がHSiO3/2基、MeHSiO基、及びH2SiO基から選ばれる基の少なくとも一種を40mol%以上有し、該ポリシロキサンの重量平均分子量が1000以上200000以下であり、該シリカ粒子の平均一次粒径が1nm以上100nm以下とする。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁信頼性の劣化を低減し、銅配線の信頼性を改善する。

【解決手段】本発明の半導体装置は、半導体基板10と、シリコン(Si)と炭素(C)と酸素(O)とを含み、半導体基板10に形成された第一の多孔質絶縁膜11a及び第二の多孔質絶縁膜11bと、第一の多孔質絶縁膜11a中に埋め込まれた第一の銅配線12aと、第二の多孔質絶縁膜11b中に、それぞれ、埋め込まれた第二の銅配線12b及び銅ビア22と、第二の銅配線12a上に形成された第一のメタルキャップ膜13aと、第二の銅配線12b上に形成された第二のメタルキャップ膜13bと、を有する。第一、第二の多孔質絶縁膜11a、11bは、少なくとも上層のC/Si比が1.5以上であり、かつ、第一、第二の多孔質絶縁膜11a、11bの少なくとも上層に含有される空孔の最大径が1.3nm以下である。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高品質のMOS構造に応用可能な、SiC材料の表面にその酸化膜であるSiO2膜が形成されてなる半導体装置を製造する方法を提供する。

【解決手段】SiC材料の表面にその酸化膜であるSiO2膜が形成されてなる半導体装置は、SiC材料の表面にソフトブレークダウン特性を示すSiO2膜を形成し、得られたSiO2膜のソフトブレークダウン特性を改善することにより製造する。具体的には、SiCからあらかじめ形成した熱酸化膜を、比較的高温で酸化種濃度が低い条件で熱処理した酸化膜、あるいは比較的高温で酸化種濃度の低い条件でSiC上に形成した酸化膜を、実質的にSiCで酸化が進行しない温度で酸化種濃度の高い条件下で熱処理すればよい。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

41 - 60 / 243

[ Back to top ]