Fターム[5F058BA01]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 高耐圧 (243)

Fターム[5F058BA01]に分類される特許

21 - 40 / 243

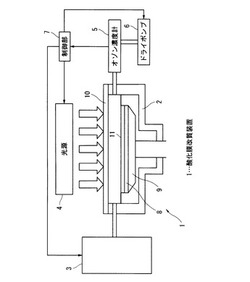

酸化膜改質方法及び酸化膜改質装置

【課題】紫外光による基板のダメージを最小限に抑えながら基板の酸化膜の改質を行う。

【解決手段】オゾンと紫外光とを基板11に供して基板11上の酸化膜を改質する酸化膜改質装置1は、格納された基板11に対してオゾンと紫外光が供される処理炉2と、前記改質が開始されてからの基板11に供された後のオゾンガスのオゾン濃度の上昇を検出しこの検出したオゾン濃度の上昇速度の変化に基づき紫外光の照射を制御する制御部7とを備える。制御部7は前記オゾン濃度の上昇速度の低下を検出した時点で基板11に対する紫外光の照射を停止させる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】窒化処理によって低下した閾値電圧を、向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】ベース領域7およびソース領域8を含む炭化珪素ドリフト層6上に二酸化珪素を主成分とするゲート絶縁膜11が形成された炭化珪素基板2を窒化処理する窒化処理工程と、窒化処理工程後、炭化珪素基板2を、一酸化二窒素を含む雰囲気中で600℃以上1000℃以下の温度で熱処理する熱処理工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】低誘電率、低エッチングレート、高絶縁性の特性を備える絶縁膜を形成する。

【解決手段】基板を収容した処理容器内にCVD反応が生じる条件下で所定元素含有ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に炭素含有ガスを供給することで、所定元素含有層の上に炭素含有層を形成して所定元素および炭素を含む層を形成する工程と、処理容器内に窒素含有ガスを供給することで、所定元素および炭素を含む層を窒化して炭窒化層を形成する工程と、を1セットとしてこのセットを所定回数行うことで所定厚さの炭窒化層を形成する工程と、処理容器内に酸素含有ガスを供給することで、所定厚さの炭窒化層を酸化して酸炭窒化層を形成する工程と、を1サイクルとして、このサイクルを所定回数行うことで、基板上に所定膜厚の酸炭窒化膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、リーク電流が小さく、かつ容量の大きい容量絶縁膜を有するキャパシタを備えた半導体装置の製造方法を提供することを課題とする。

【解決手段】容量絶縁膜形成工程は、下部電極が形成された半導体基板を成膜装置内に設置する工程と、半導体基板の温度を第1の温度に保持する第1の温度調整工程と、下部電極を覆うように、第1の温度に保持された半導体基板上に第1の絶縁膜を成膜する第1の成膜工程と、半導体基板を第2の温度に保持する第2の温度調整工程と、第1の絶縁膜の表面を覆うように、第2の温度に保持された半導体基板上に第2の絶縁膜を成膜する第2の成膜工程と、第1の温度調整工程、第1の成膜工程、第2の温度調整工程、第2の温度調整工程、及び第2の成膜工程を繰り返し行うことで、前記容量絶縁膜を形成する繰り返し工程と、を含む。

(もっと読む)

キャパシタ及び半導体装置

【課題】高い絶縁破壊耐圧のMIMキャパシタを提供する。

【解決手段】半導体基板上に形成された下部電極12と、前記下部電極上に形成された第1の絶縁体膜13と、前記第1の絶縁体膜上に形成される第2の絶縁体膜14と、前記第2の絶縁体膜上に形成される第3の絶縁体膜15と、前記第3の絶縁体膜上に形成される上部電極16と、を有し、前記第1の絶縁体膜における密度は、前記第2の絶縁体膜における密度よりも高く、前記第3の絶縁体膜における密度は、前記第2の絶縁体膜における密度よりも高いことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】微小化されたトランジスタはゲート絶縁層の薄膜化を要求されるが、トンネル電流、つまりゲートリーク電流の増加により、ゲート絶縁層が酸化珪素膜の単層である場合はゲート絶縁層の薄膜化には物理的限界が生じつつある。

【解決手段】ゲート絶縁層に比誘電率が10以上のhigh−k膜を用いることで、微小化したトランジスタのゲートリーク電流を低減させる。酸化物半導体層と接する第2の絶縁層よりも比誘電率が高い第1の絶縁層としてhigh−k膜を用いることによって、酸化珪素膜で換算した場合のゲート絶縁層よりもゲート絶縁層の薄膜化ができる。

(もっと読む)

低誘電率層間絶縁膜および低誘電率層間絶縁膜の成膜方法

【課題】低誘電率化と、絶縁膜破壊、エレクトロマイグレーションやストレスマイグレーションの抑制という性能を備える低誘電率層間絶縁膜および低誘電率層間絶縁膜の成膜方法を提供する。

【解決手段】プラズマCVD法によって形成された低誘電率層間絶縁膜であって、珪素に対する炭素の比率が2.5以上であり、かつ比誘電率が3.8以下であることを特徴とする低誘電率層間絶縁膜を採用する。また、プラズマCVD法によって、珪素に対する炭素の比率が2.5以上であり、かつ比誘電率が3.8以下である低誘電率層間絶縁膜の成膜方法であって、前記プラズマCVD法によって成膜する際に、絶縁膜材料として炭化水素を用いないことを特徴とする低誘電率層間絶縁膜の成膜方法を採用する。

(もっと読む)

薄膜トランジスタ基板

【課題】透明導電膜を配線電極とした場合における段差部での絶縁不良や断線を解決し、酸化物半導体膜が持つ高い移動度を生かした高速応答ディスプレイや周辺回路等を実現することができる、薄膜トランジスタ基板を提供する。

【解決手段】基材1と、基材1上に設けられた透明導電膜からなるゲート電極2と、ゲート電極2を覆って平坦化するように設けられたゲート絶縁膜3と、ゲート電極2の上方であって前記ゲート絶縁膜3上に設けられた酸化物半導体膜4と、酸化物半導体膜4上に該酸化物半導体膜4の中央部を開けて離間して設けられたソース電極5s及びドレイン電極5dとを有し、前記ゲート絶縁膜3が、塗布型材料からなる絶縁性の平坦化膜3aを有するように構成した。ゲート絶縁膜3は、平坦化膜3aからなるように構成してもよいし、平坦化膜3aと平坦化膜3a上に設けられた絶縁膜3bとからなるように構成してもよい。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

絶縁膜の形成方法

【課題】絶縁膜としての性能を損なうことなく、スピンオングラスを用いた簡便な方法でメタル下絶縁膜や素子分離用絶縁膜として利用可能な絶縁膜を形成する方法を提供する。

【解決手段】第一の工程としてオルガノアルコキシシランの加水分解縮合物を含む塗布液を基板上に塗布して塗布基板を得る工程と、第二の工程として前記塗布基板を700℃以上900℃以下の温度で水素を含む気体中で加熱して前記塗布膜を焼成して絶縁膜を形成する焼成工程とを順に含む。

(もっと読む)

平坦化後の高密度化

パターン付き基板上に高密度の間隙充填酸化ケイ素を形成するプロセスについて記載する。このようなプロセスは、特に狭いトレンチ内で間隙充填酸化ケイ素の密度を増大させる。密度は、広いトレンチおよび凹んだ開放領域内でも増大させることができる。処理の後では、狭いトレンチと広いトレンチ/開放領域内の間隙充填酸化ケイ素の密度は互いに接近し、エッチング速度の一致度が高まる。この効果は、パターンローディング効果の低減として説明することもできる。このプロセスは、酸化ケイ素を形成し、次いで平坦化するステップを伴う。平坦化により、狭いトレンチに近接して配置された新しい誘電体インターフェースが露出する。新しく露出されたインターフェースは、平坦化された表面をアニールし、かつ/またはプラズマに露出させることによって、高密度化処理を容易にする。  (もっと読む)

(もっと読む)

絶縁膜形成方法、絶縁膜形成装置及び半導体装置

【課題】半導体基板に対し簡易な手法により均質な絶縁膜を高速に形成できるようにする。

【解決手段】絶縁膜形成装置1は、堆積部10の電子ビーム蒸着源12からハフニウム金属の原子線を照射して、基板70のシリコン酸化膜72上に液体状のハフニウム微粒子73を堆積させて堆積状態とし、照射部20のプラズマ源22から窒素原子、活性窒素分子及び窒素イオンでなる活性粒子74を照射することにより、表面に窒化ハフニウムシリケート膜76を形成すると共にシリコン酸化膜72をシリコン酸窒化膜75に変化させ、基板70を成膜状態とする。この結果絶縁膜形成装置1は、基板70へのハフニウム微粒子73の堆積処理及び窒素プラズマでなる活性粒子74の照射処理を行うことにより、高誘電率ゲート絶縁膜として機能し得る窒化ハフニウムシリケート膜76を短時間で容易に形成することができる。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】TiO2膜とHfO2膜との相互拡散を抑制でき、リーク電流の増加を抑制させる。

【解決手段】基板上に第1の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜上に絶縁膜を形成する工程と、絶縁膜上に第2の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜が形成された基板に対して熱処理を行う工程と、を有し、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜は、それぞれが異なる物質で構成されると共に、絶縁膜は、酸化アルミニウム膜、窒化アルミニウム膜、または、窒化シリコン膜で構成される。

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

絶縁膜およびその製造方法、半導体装置、ならびにデータ処理システム

【課題】誘電率が大きく、電極間に挟んで用いてもリーク電流値の小さい絶縁膜を提供する。

【解決手段】結晶化した酸化ジルコニウムからなる酸化ジルコニウム膜の2つと、非晶質であって、前記結晶化した酸化ジルコニウムよりも大きい誘電率を有する材料からなる結晶粒界分断膜とを有し、前記結晶粒界分断膜が、前記2つの酸化ジルコニウム膜に挟まれている絶縁膜を形成する。例えば、上部電極と下部電極の間に容量絶縁膜を有するキャパシタ素子で構成されたメモリセルを備える半導体装置における容量絶縁膜や、コントロールゲート電極とフローティングゲート電極の間にインターゲート絶縁膜を有する不揮発性メモリ素子を備えた半導体装置におけるインターゲート絶縁膜として好適である。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン表面に厚さがサブナノから数ナノメートル(nm)レベルの極薄の絶縁膜を形成し、これを利用して、低電圧動作MOSデバイスを実現する。

【解決手段】ガラス基板上の多結晶シリコン(薄膜)に対して、その上に室温硝酸酸化法により1.8nmのSiO2膜1を形成し、さらに、その上にプラズマCVD法により40nmのSiO2膜2を堆積して積層にし、これをゲート絶縁膜10として、p−チャンネルMOSトランジスタ(TFT)を創製した。このTFTは、駆動電圧を3Vに低減しても十分に動作可能であり、消費電力を顕著に低減することできる。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上に複数のゲート絶縁膜を有する半導体装置において、例えばコア部におけるHPトランジスタの高速性の確保と、例えばI/Oトランジスタ及びLPトランジスタのゲート耐圧の向上やゲートリーク電流の低減とを両立する。

【解決手段】半導体装置は、半導体基板11上に形成された複数のゲート絶縁膜を備えており、複数のゲート絶縁膜のうち、HPトランジスタ形成領域1Cにおける膜厚が最も薄いゲート絶縁膜は、シリコン酸化膜20よりなり、I/Oトランジスタ形成領域1A及びLPトランジスタ形成領域1Bにおける残りのゲート絶縁膜は、シリコン酸窒化膜16、17よりなる。

(もっと読む)

21 - 40 / 243

[ Back to top ]